3GPP 内核算法KASUMI的IP设计与测试

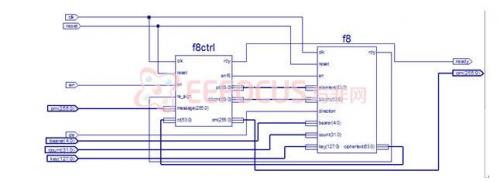

加密,f8控制器和f8共同构成了f8加密系统,系统电路图如图12所示:

图12 f8的加密系统

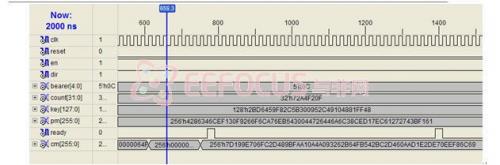

f8加密系统的测试数据如下图13所示:

输入控制信号:reset = 0 en = 1

输入数据信号:dir = 1

bearer = 01100

count = 72A4F20F

key = 2BD6459F82C5B300952C49104881FF48

pm = 4286346CEF130F92 66F6CA76EB543004 4726446A6C38CED1

7EC61272743BF161

说明:以上明文是输入到f8控制器中,f8模块还是只能一次性加密64比特的数据,通过控制其后可以一次性加密256比特的数据。复位信号reset保持无效状态,使能信号en保持有效状态。数据接收完之后,大约在第760纳秒时数据加密完成,提示信号ready输出一个高电平,同时输出加密结果。

图13 f8加密结果

5 KASUMI算法硬件测试

主要阐述KASUMI算法在Xilinx开发板上进行测试时的结果。

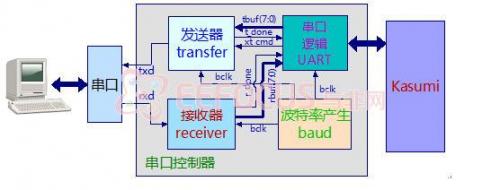

5.1 UART介绍

UART(Universal Asynchronous Receiver Transmitter 通用异步收发器)是广泛使用的串行数据传输协议。UART允许在串行链路上进行全双工的通信。在硬件上进行数据测试时,KASUMI IP核与计算机之间的串行外设用的是RS232 –C串行接口。但一般的UART器件都增加了很多的辅助功能,使得芯片十分复杂。所以在设计中使用的是自行设计的UART器件,只将所需的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。图14为UART的设计原理图 。

图14 UART原理图

5.1.1 UART器件模块功能介绍

⑴ UART发送器

发送器每隔16个BCLK时钟周期输出1位,次序遵循1位起始位、8位数据位、无校验位、1位停止位。

串口逻辑给出Xt_cmd信号,通过发送移位寄存器tbuf[7..0]发送串行数据至串行数据输出端txd。在数据发送过程中用输出信号t_done作为标志信号,当一帧数据发送完毕时,t_done信号为1,通知串口控制逻辑在下个时钟装入新数据。

⑵ UART接收器

串行数据帧和接收时钟是异步的,发送来的数据由逻辑1变为逻辑0可以视为一个数据帧的开始。接收器先要捕捉起始位,确定rxd输入由1到0,逻辑0要15个Bclk时钟周期,才认定是正常的起始位,然后在每隔16个bclk时钟周期采样接收数据,移位输入接收移位寄存器rbuf,数据接收完后输出一个数据接收标志信号标志r_done。

⑶ 波特率发生器

UART的接收和发送是按照相同的波特率进行收发的。波特率发生器产生的时钟频率不是波特率时钟频率,而是波特率时钟频率的16倍,目的是为在接收时进行精确地采样,以提取出异步的串行数据。

5.1.2 UART器件FPGA实现

串口通讯模块是位于FPGA内部的负责与计算机进行数据传输的一个控制逻辑模块,因此它所要实现的主要任务是从计算机接收数据以及将数据发送到计算机。在设计中,有一个顶层的串口通讯控制单元uart,它向下调用了baud、receive、transter元件设置了数据传输的波特率并控制了数据的收发进程。根据我们的设计,上位机与下位机之间以通讯速率9600bps/s传输数据,无奇偶校验,八位数据位和一位停止位。具体的实体定义和程序如下所示:

------------------------------------串口通讯模块实体定义---------------------------------------

entity uart is

generic (xbit: integer:=64; --明文长度

ybit: integer:=64; --密文长度

kbit: integer:=128; -密钥长度

div:integer:=325 --波特率分频比

);

Port(

clk50mhz, --时钟

reset, --复位

rxd, --rxd数据接收线

xt_en :in std_logic; --数据流向线,1为发送,0为接收

Y_reg :in std_logic_vector(ybit-1 downto 0) ; --密文输入

txd, --txd数据发送线

txd_ok, --数据发送完毕信号

rxd_ok : out std_logic; --数据接收完毕信号

X_reg : out std_logic_vector(xbit-1 downto 0); --明文

K_reg : out std_logic_vector(kbit-1 downto 0) --密钥

);

end uart;

-----------------------------------------串口通信处理程序----------------------------------------------

r:process(r_re,rese

3GPP 内核算法 FPGA KASUMI IP设计 相关文章:

- 全球WiMAX论坛主席Ronald Resnick演讲(08-23)

- NGN之路:十字路口的思考(01-10)

- 下一代网络中的SIP-I协议(01-27)

- NGN SIP 域内的标准化(01-27)

- 朗讯IMS:NGN融合的引擎(01-01)

- 亚太将成IPv6下个热点地区?(01-01)