3GPP 内核算法KASUMI的IP设计与测试

状态。定义如下:

type d_state is (nothing,kasumi,done);

其中,加密状态中进行KASUMI的8轮迭代加密,完成整个数据加密过程。通过改进,使得算法由原来的8个状态缩减为3个状态,节省了很大一部分资源,使得编译速度提升了近13倍 。

3.2.3 方案资源占用比较

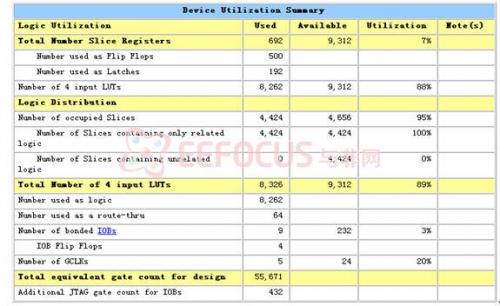

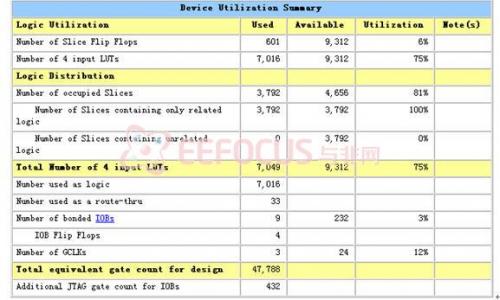

经过ISE仿真,可以得到两种设计方案的资源占用情况。如图6、图7所示。由图中的数据可以看出:方案一中,slice寄存器占用7%、slice占用95%、4输入逻辑查找表占用89%、整个设计的等效门数为55671;方案二中,slice寄存器占用6%、slice占用81%、4输入逻辑查找表占用75%、整个设计的等效门数为47788。通过比较可以发现,第二种设计方案的资源占用情况有明显的减少,在编译时,速度也有了明显的提升。

图6 方案一资源占用表

图7 方案二资源占用表

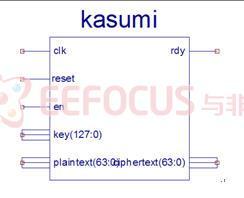

3.3 KASUMI IP核的引脚定义及模型

KASUMI模块的设计中包含5个输入和2个输出。以下为输入输出端口说明:

· 时钟信号 clk

· 复位信号 reset 高电平有效

· 使能信号 en 高电平有效

· 加密密钥 key 128bit

· 明 文 plaintext 64bit

· 完成信号 rdy 高电平有效

密 文 ciphertext 64bit

KASUMI IP核如图8所示:

图8 KASUMI的IP核

3.4 f8软核的实现方案论证

f8算法的基础是KASUMI算法,他根据明文的长度来决定调用KASUMI加密模块的次数,从而生成与明文等长的密钥流。所以设计f8算法首先要解决的问题是决定调用KASUMI加密模块的次数。

3.4.1 方案一

调用2次KASUMI加密模块。首先,生成寄存器A中的初始值时调用一次,然后根据输入的明文的长度进行状态循环,在循环中再调用一次KASUMI加密模块,从而输出密钥流。由于KASUMI模块是以函数的形式进行调用的,占用很多资源,调用次数越多,编译速度越慢。经测试,调用2次KASUMI加密模块资源占用率超过了100% 。

3.4.2 方案二

只调用1次KASUMI加密模块。通过判断输入的值是否为初始化值,成功的省去了生成寄存器A中的值时调用的那一次KASUMI加密模块,只调用一次KASUMI加密模块,减小了资源占用率,使其降至89% 。这样即可实现f8算法的软核。

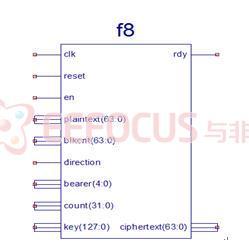

3.5 f8核的引脚定义及模型

f8模块的设计中包含9个输入和2个输出。以下为输入输出端口说明:

· 时 钟 信 号 clk

· 复 位 信 号 reset 高电平有效

· 使 能 信 号 en 高电平有效

· 加 密 密 钥 key 128bit

· 明 文 plaintext 64bit

· 计 数 器 blkcnt 64bit

· 方 向 控 制 directions 1bit

· 无 线 承 载 bearer 5bit

· 基于时间的输入 count 32bit

· 完 成 信 号 rdy 高电平有效

· 密 文 ciphertext 64bit

f8核如图所示:

图9 f8的IP核

4 KASUMI及f8算法的FPGA优化设计及仿真

主要阐述KASUMI算法以及f8算法的FPGA实现及优化的过程。

4.1 开发环境ISE

FPGA设计工具的种类繁多,在本设计中使用的是Xilinx的FPGA,ISE是其必备的设计工具。ISE可以完成FPGA开发全部的流程,包括设计输入、仿真、综合、布局布线、生成BIT文件、配置以及在线调试等,功能非常强大。同时ISE继承了大量的实用工具,包括HDL编辑器HDL Editor、IP核生成器CORE Generator System、约束编辑器Constraints Editor、静态时序分析工具Static Timing Analyzer、布局规划工具FloorPlanner、FPGA编辑工具FPGA Editor和功耗分析工具Xpower等,这些工具可以帮助设计人员完成设计任务并提高工作效率。

4.2 对模块的描述及仿真

4.2.1 KASUMI模块的ISE仿真及测试

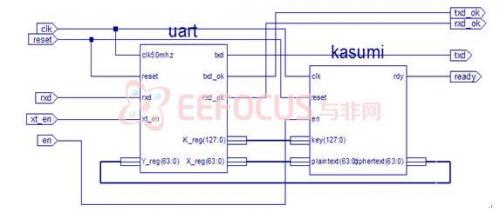

图10为KASUMI加密系统的电路图:

图10 KASUMI的加密系统

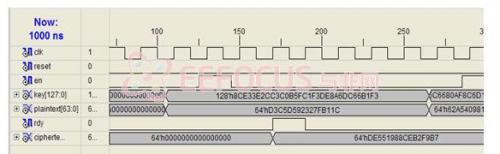

图11为测试数据:

加密密钥:key=8CE33E2CC3C0B5FC1F3DE8A6DC66B1F3

明 文:plaintext=D3C5D592327FB11C

说 明:复位信号保持0状态,使其无效。在第3个时钟时,令使能信号en有效,这时明文和密钥被送入加密系统中进行加密。在第6个时钟时,加密完成,rdy信号给出指示,同时输出密文。

图11 KASUMI加密结果

4.2.2 f8模块的ISE仿真及测试

使用控制器来控制f8,即可一次性输入256比特的数据,对数据进行

3GPP 内核算法 FPGA KASUMI IP设计 相关文章:

- 全球WiMAX论坛主席Ronald Resnick演讲(08-23)

- NGN之路:十字路口的思考(01-10)

- 下一代网络中的SIP-I协议(01-27)

- NGN SIP 域内的标准化(01-27)

- 朗讯IMS:NGN融合的引擎(01-01)

- 亚太将成IPv6下个热点地区?(01-01)