一种简单灵活的PLL设计

本设计思想中的简单电路给出了一个传统模拟锁相环的基础特性,但电路中除了基准振荡器以外,没有其它的模拟元件。虽然其它可用的数字PLL,包括那些采用加/减计数器的数字PLL,但本文这个更简单也更灵活。

此电路最早在30多年前用作时钟再生器,用于磁记录中自带时钟码(如曼彻斯特码或双相码)的数据分隔器。很快人们就明白了它有很多其它应用。该电路亦可以作为伺服控制器的基础,用于磁带驱动器的走带轮电机/转速计。LSI磁盘/磁带控制芯片同时包括了数据分隔器和走带轮伺服控制器,其优点是没有模拟电路,不需要调节。由于它很早以前就已用于批量的产品中,因此今天已没有专利问题,可以免费使用。

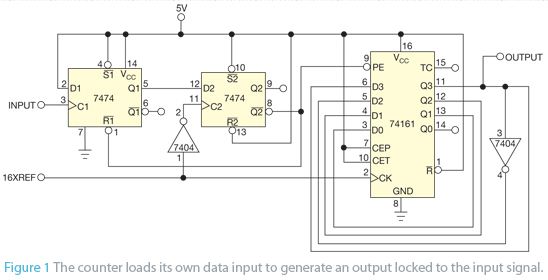

图1中的例子只使用了三只IC,可快速制作出原型电路,解释也很简单。74161计数器输出与预置输入端之间的连接,构成了一个实现查询表的基本ROM(表1)。16XREF应是一个方波,或至少不是一个窄脉冲,因为必须考虑在上升沿和下降沿以及设置时间出现的情况。INPUT脉冲必须足够长,以满足为7474 D触发器所挑选逻辑系列器件对时钟脉冲宽度的要求。

图1 计数器装入自己的数据输入,从而产生一个锁定到输入信号的输出。

在原型测试时,使INPUT大约为16XREF频率的1/16,当缓慢改变INPUT频率时,查看输出。使用一台能够精细调节INPUT的信号发生器,测量1/16 XREF源的略偏上和偏下处的锁定范围。抖动等于16XREF的时钟周期,但当INPUT变化为±20%或更多时,输出会保持锁定住INPUT。当频率互相接近时,可以临时断开计数器的Pin 9,观察输出滑过INPUT。重新连接Pin 9可证明锁定动作。当INPUT是16XREF的精确1/16时,输出为方波,当高于或低于中心频率时,输出会成为长方形。

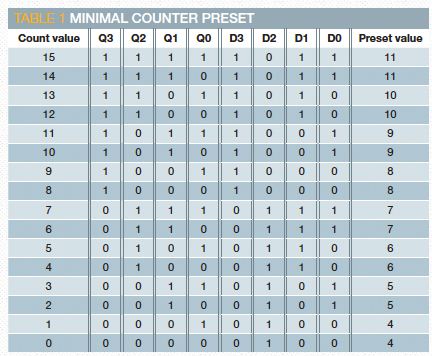

表1 最小计数器预置

运行时,计数器连续计数,但INPUT信号的每个上升沿都会在计数器产生一个预置脉冲。从表1的计数与预置值,可以推测出,每当计数器得到一个预置脉冲,计数就会更接近于7或8。如果它已经是7或8,则就会保持不变。伺服循环误差信号是在预置信号到达的时刻,计数器当前状态与7或8之间的差。这个简单例子使用了计数值,将用于预置的误差信号减半。

如果INPUT信号是基准的精确1/16,但起始的相位差180°,则第一个预置脉冲可能在计数器为15时出现。于是,计数器预置为11,从这里恢复计数。在下一个预置脉冲时,计数器为10,预置到9。接下来的预置脉冲出现在计数为8时,并预置到8。然后会预置到7;当计数器为6下一个预置脉冲到来时,它再次预置为7,现在就同步了。预置脉冲恰于计数器的最高有效位从0变1时到来,这也是INPUT信号正在做的动作。

如果INPUT信号略慢于基准的1/16,则当计数器计到超过8时(如到12),预置脉冲到来。它将预置值设为10。但由于INPUT信号太慢,当下个预置脉冲到来时,计数器再次回到12。电路仍然锁定,但MSB会延长以适配于较慢的INPUT信号。对于快于1/16基准的INPUT信号,相同过程维持着锁定,但MSB信号的周期缩小,以维持锁定。

如果INPUT过慢,计数器超过了15并返回到0,或在预置发生以前就超出,则发生失锁情况。如果在下一个预置脉冲到来以前,计数器甚至不能计数到0,也很可能会失锁。电路可以锁定在16X基准的倍数或约数上。

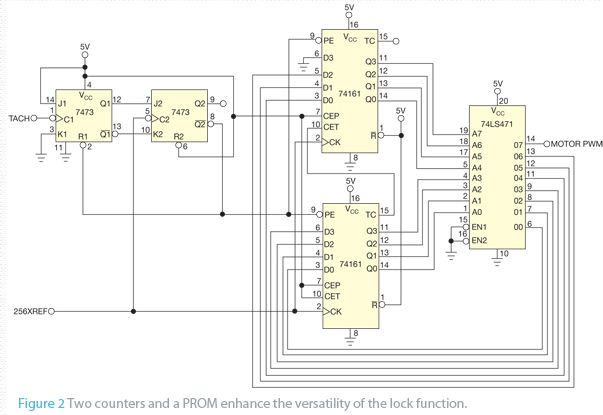

可以对锁定特性作一些调整,增加更多的计数器位,在计数器输出端与预置的输入端之间放一个ROM,减少抖动(图2和图3)。例如,使用一只PROM,可以将误差除以3或4,增加锁定区间。另外,还可以用一只PROM,将误差信号减1或减2,而不是将误差除以2。这种方法可明显收窄锁定区间。PROM的多余输出线(不用于计数器预置)还可以用于其它功能。

由于计数器的预置脉冲出现于有误差信号的那个时刻,因此可以在PROM里写更多的位,锁存供其它应用使用的错误条件,如指示一个未锁存的状态,或指示INPUT频率相对于基准信号的高、低或正中。这种方法用于电机控制器时,可以指出电机的负载是轻、中等还是重。对于其它应用,可以编写第二个并行PROM,将采样送给一个DAC而生成一个正弦波,或为一个电源转换器生成一个准正弦波。

图2 两个计数器和一个PROM增强了锁定功能的多用性。

作为走带轮电机伺服控制器时,转速计是给PLL的INPUT,而电机速度锁定到晶体的基准频率。PROM的一个输出位(针对电机PWM信号作了修正)使伺服控制更好地控制占空比。预置的MSB为0,迫使系统在锁定情况下,工作在下半地址空间内。这种方案空出了PROM的最高输出线,使之成为电机控制信号。

图3 用示波器中上方轨迹的输入信号作触发,可以在示波器的下面轨迹看到被锁定的输出信号抖动。

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 全数字锁相环的设计及分析(03-01)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环中YTO自校准技术的应用(10-02)

- 基于DDS+PLL技术的频率合成器的设计(07-23)

- 锁相环在反馈电路上的应用(01-10)