开关电容滤波器的系统设计与实现

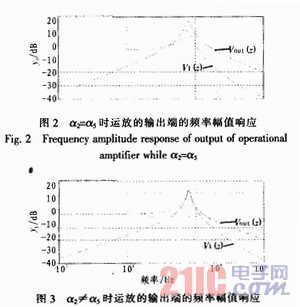

这里需要说明的是,图l所示的低Q值开关电容二阶带通滤波器用到了两个运放,其输出端口分别为V1(z)和Vout(z)。其中V1(z)对应低通滤波特性(如图2下方曲线),Vout(z)对应带通滤波特性(如图2上方曲线),其增益峰值都在滤波器的中心频率ω0处获得。为了在滤波器内部得到最大的动态范围,需要在中心频率ω0处V1(z)和Vout(z)相等,分别求得V1(z)和Vout(z)对应于Vin(z)的传输函数,并计算函数对应于中心频率ω0处的取值。计算方法很简单,将s=jω0分别代入传输函数V1(z)和Vout(z)即可。不难发现,在中心频率ω0处,当且仅当α2=α5时,有V1(z)=Vout(z)。图2和图3分别通过仿真分别给出了α2=α5时与α2≠α5时两个运放的输出端的频率幅值响应。仿真结果也很好验证了低Q结构更适合该滤波器设计要求。

3 运算放大器的设计

运算放大器是开关电容滤波器中重要的元件。如果运算放大器的指标不合理,可能会影响到整个滤波器的性能。所以需要根据实际的滤波器的性能要求选择适当的运放指标,从而使整个系统满足要求。该滤波器的设计指标如表1所示。

对于给定指标的运算放大器,合理的结构选择是整个设计中最为关键的一点。在考虑指标实现的同时,还需要考虑到可实现性,同等情况下选择更简单、版图更小的结构。选择一级运放。因为其负载电容就是补偿电容,无需特意去增加补偿电容,而且相对于二级运放(一般用米勒补偿),一级运放在电源抑制比等方面都有优势。

4 软件设计

系统控制主要包括输入仪表放大器控制、峰值检测控制、开关电容滤波器控制、增益控制、滤波器通道控制、输出反相控制、键盘控制、显示控制等部分。这里主要介绍开关电容滤波器的控制。开关电容滤波器的控制包括时钟发生模块和编程参数控制模块2部分。时钟发生模块用于生成的各个二阶滤波器组件的时钟信号,该可编程滤波器系统共需3路时钟控制。滤波器编程参数控制模块用于实现芯片内部程序存储器编程控制,包括滤波器编程参数读取模块和接口时序控制模块。

4.1 时钟发生模块

时钟信号发生器模块由频率跟踪检测、参数读取、除法器、分频器和时钟使能控制等部分构成。

1)频率跟踪检测 滤波器在跟踪工作模式下,PLC需检测信号的周期。对输入脉冲周期进行计数,将一个输入信号周期所占的时钟周期数输出给参数读取模块进行处理,程序较为简单。

2)参数读取 根据滤波器类型、滤波器逼近函数和滤波器阶数生成ROM的读取地址。滤波器在典型和跟踪工作模式下选择对应的ROM读取除法器的被除数或除数;手动工作模式下,被除数为常数,除数直接从按键的键值输入缓冲区读取。由于系统使用2片MAX260,需要4路时钟,故要读出4组被除数和除数。图4为参数读取模块的仿真波形,图中的z1_f,z2_f,z3_f,z4_f为4组被除数,d1_f,d2_f,d3_f,d4_为4组除数。

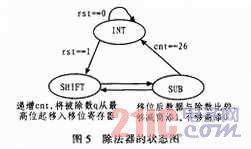

3)除法器 由于PLC采用50 MHz的晶振,输入的中心频率(或截止频率)最大为4 kHz,因此采用26位除法器。由于PLC的除法指令需要占用很大资源,本设计采用移位相减实现除法运算。除法器的状态图如图5所示,除法器的算法如下:将被除法从高位开始移入移位寄存器的低位,移位寄存器每移位一次后与除数相减,结果大于零则商置1,将相减得到的结果后接还未移入移位寄存器的被除数再左移;结果小于零,则商置零,将原被减数后接还未移入移位寄存器的被除数再左移。如此移位相减直至被除数全部位数判断完成,即移位相减26次以后,除法完成。

4)分频器模块和时钟使能 分频器从除法器的结果作为分频系数对PLC的时钟频率分频,得到各个二阶滤波器组件的时钟信号。时钟信号产生后并不马上送入MAX260的时钟输入引脚,需检测到MAX260的编程代码下载完成后再使能时钟输出,下载过程中,时钟信号保持高阻态,且对未使用的二阶滤波器组件,其时钟信号亦保持高阻态。

4.2 滤波器编程参数控制

本系统中滤波器在典型和跟踪工作模式下的逼近函数是确定的,故其编程代码也是确定的,将编程代码存入存储器中,根据滤波器的各参数读取编程代码即可。手动模式下,编程参数由外部输入。为方便下载,将4个二阶滤波器节组件的编程代码组成一个64位的编程控制字。每种逼近函数的各阶低通、高通和带通滤波器对应一个64位的编程控制字,故

- DC-DC电荷泵的研究与设计(01-05)

- 基于开关电容共模反馈理论分析(05-30)

- 开关电容梳状滤波器幅频特性的深入分析(06-05)

- 高效率谐振型开关电容变换器(08-04)

- 有源滤波器与开关电容滤波器的性能比较(08-13)

- 开关电容滤波器前后置滤波器的配置与设计(02-22)