并联ADP1763 LDO稳压器以支持高输出电流应用

许多高性能混合信号产品,如高速模数转换器(ADC)和数模转换器(DAC)、捷变射频(RF)收发器、时钟、专用集成电路(ASIC)和现场可编程门阵列(FPGA)等,需要超低噪声、低压差(LDO)线性稳压器来提供干净电源,从而最大程度地提高信号链性能。对更多集成功能和更低功耗的高要求,使得这些大规模混合信号集成电路(IC)的设计工艺尺寸越来越小(例如28 nm或更小),以便容纳更多晶体管。这种趋势同样影响了电源要求。近年来,内核电源电压持续降低,但为了支持更多模拟或数字功能,负载电流显著提高(例如3 A以上)。

在特定应用中,要找到能同时满足超低噪声和高负载电流这两个设计目标的合适LDO稳压器是相当困难的,因为市场上的LDO稳压器产品非常有限,即使有合适的器件,用户也可能要支付额外的费用。因此,针对高电流应用,有时候将LDO稳压器并联起来会很有利。在高负载应用中,相比于单个LDO稳压器,并联LDO稳压器具有许多优势,包括热量和功率损耗会分配在多个LDO稳压器封装上。另外,并联LDO稳压器还能改善压差,提高电源抑制比(PSRR)性能,因为与单个LDO稳压器相比,各LDO稳压器的工作电流更低。图1所示为一个高性能混合信号产品的电源图。两个ADP1763器件并联以提供内核电压,如图1所示。

图1.混合信号产品电源图

本应用笔记介绍两种并联方法:无源和有源。对于无源并联,两个可调ADP1763器件通过镇流电阻并联在一起。对于有源并联,一个低失调轨到轨放大器ADA4051-1调节ADP1763器件的输出电压,通过检测两个ADP1763器件的电流差来实现均流。实验测试结果显示了两种方法的优点和缺点。

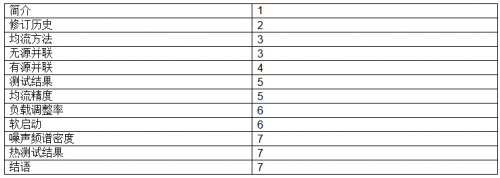

目录

修订历史

2016年10月-修订版0:初始版

均流方法

一般而言,用户简单地将两个LDO稳压器并联是不能实现均流的,由于容差,两个LDO稳压器的输出电压可能不匹配;比如LDO基准电压不同、反馈电阻不一致、印刷电路板(PCB)寄生特性不一致等。LDO稳压器的输出电压不匹配可能引起负载电流严重不平衡。在最不利情况下,它可能导致一个LDO承受大部分负载,从而触发限流保护。

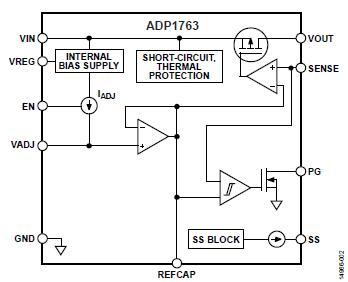

ADP1763是一款LDO线性稳压器,采用单输入电源工作,输入电压低至1.1 V,无需外部偏置电源,提供高达3 A的输出电流。ADP1763的输出噪声非常低,在100 Hz至100 kHz范围内仅有2 μV rms。ADP1763的超低输出噪声特性是通过如下方法实现的:LDO误差放大器保持单位增益,并设置基准电压等于输出电压。单位增益架构的优势是LDO输出噪声与输出电压设置无关。更多信息参见图2。

图2.ADP1763内部框图

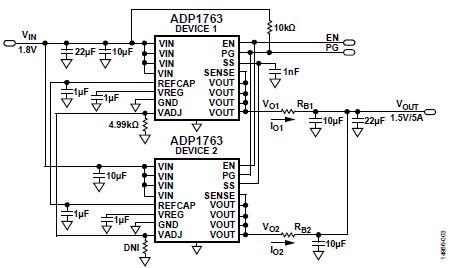

无源并联

一种实用的均流方法是在各稳压器的输出端增加相同的镇流电阻(RB1和RB2),以改善多个LDO稳压器之间的均流性能。为了实现更好的均流性能,最好使用高阻值镇流电阻。然而,高电阻会降低负载调整性能,使得压差变大。设计时必须权衡考虑以选择合适的镇流电阻,扬长避短。图3显示两个ADP1763器件并联。为使输出误差最小,应将各自的REFCAP和VADJ引脚连起来,以在不同器件上实现精密匹配的基准电压。将各自的SS和EN引脚连起来,以在不同器件之间实现同步软启动行为。如果应用需要电源良好指示功能,还应将其PG引脚连起来。

当两个ADP1763器件的REFCAP引脚相连时,主要输出电压误差来源于误差放大器失调电压,误差放大器连接到各ADP1763输出。此误差放大器的失调电压非常低,在−40°C至+125°C温度范围内其最大值为±1.32 mV。REFCAP引脚和VOUT引脚之间仅有±1.32 mV误差,此失调电压允许使用小镇流电阻来实现合理的均流精度。此外,小镇流电阻还有低负载调整率和低功率损耗的优势。

为了计算最差情况,假设VO1具有最差正失调电压,VO2具有最差负失调电压。

VO1 = VREFCAP + VOFFSET

VO2 = VREFCAP − VOFFSET

总输出电流(IO) = 5 A,IO = IO1 + IO2。

图3.两个ADP1763器件无源并联

镇流电阻容差(RS-TOL)为±1%。为了计算最差情况,假设VO1电压轨上的镇流电阻具有正容差,VO2电压轨上的镇流电阻具有负容差。

VO1 − IO1 × RB × (1 – RS-TOL) = VO2 − IO2 × RB × (1 + RS-TOL)

当RS-TOL = 1%时,

其中,CSACCURACY为均流精度。

图4显示了5 A负载时均流精度和压降与镇流电阻阻值的关系。均流精度随着镇流电阻阻值提高而提高。然而,代价是压降变大。为了实现大约10%的均流精度和最小压降,选择RB = 5 m?。

图4.均流(CS)精度和压降与镇流电阻的关系

基于图4中的计算,5 A负载时最差情况下的均流精度为±11.6%。最大负载电流为2.

- 系统级电源管理对可携式产品的重要性(10-07)

- 极点跟随的LDO稳压器频率补偿方法的研究(02-11)