锁相环中YTO自校准技术的应用

时间:10-02

来源:互联网

点击:

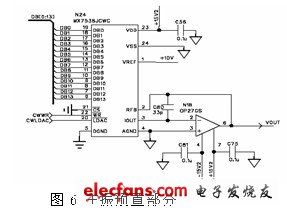

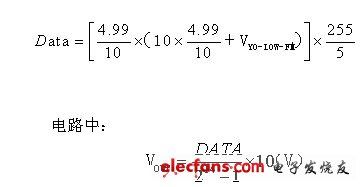

20GHz全频段能有较为精细的预置分辨率,并且满足△Data插值需要,在此选择了14位D/A转换器,使用时在数据范围0~16383两端预留一定的插值空间,电路如图6所示。

该电压加到低频驱动电路,即可实现对频率的预置补偿。

4 应用分析

对于不同批次的YTO,其非线性特性不尽相同,而对应于不同的驱动电路,提供的线性驱动电压准确度也有区别,因此,针对全频段的预置误差实时取样实时补偿的自校准技术,很好地弥补了这种不同个体间的差异性,省却了逐一测试预置频率误差的麻烦;而采取在主振预置电路叠加误差数据的补偿方式,使外加硬件补偿电路并非必需,从而节省了设计成本,调试起来也更加方便。

一般来说,实际调试中可以通过预调合适的线性驱动电压,使YTO初始化预置频率在环路的捕获带宽以内,达到一次扫描过程中的初始锁定状态。由于同步带宽远大于捕获带宽,那么锁住起始点后,在锁定状态下向后搜索相邻的校准点,将允许在更大的预置误差下获取补偿数据。因此,理论上讲,一次扫描就可以实现对YTO在全频段内的校准。当然,实际工程应用中,为了防止漂移,还可通过设置合理的误差门限范围,进行几次循环补偿,使预置更加精准。

另外,由于YTO预置的渐变性,校准过程中可以利用当前频率点的误差补偿数据作为相邻频率点的预补偿,将进一步降低了搜索下一个校准点时的失锁危险,也是快速完成该校准过程的技巧之一。

5 结论

这种环路自校准技术也可以延伸到功率补偿的应用方面。

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 全数字锁相环的设计及分析(03-01)

- 基于锁相环的频率合成电路设计(07-30)

- 基于DDS+PLL技术的频率合成器的设计(07-23)

- 锁相环在反馈电路上的应用(01-10)

- 一种简单灵活的PLL设计(07-11)