移相控制全桥ZVS-PWM变换器的分析与设计

上世纪60年代开始起步的DC/DC PWM功率变换技术出现了很大的发展。但由于其通常采用调频稳压控制方式,使得软开关的范围受到限制,且其设计复杂,不利于输出滤波器的优化设计。因此,在上世纪80年代初,文献提出了移相控制和谐振变换器相结合的思想,开关频率固定,仅调节开关之间的相角,就可以实现稳压,这样很好地解决了单纯谐振变换器调频控制的缺点。本文选择了全桥移相控制ZVS-PWM谐振电路拓扑,在分析了电路原理和各工作模态的基础上,设计了输出功率为200W的DC/DC变换器。

1 电路原理和各工作模态分析

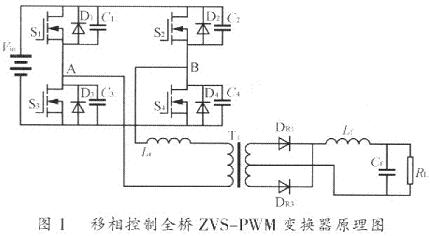

1.1 电路原理

图1所示为移相控制全桥ZVS-PWM谐振变换器电路拓扑。Vin为输入直流电压。Si(i=1.2.3,4)为第i个参数相同的功率MOS开关管。Di和Gi(i=l,2,3,4)为相应的体二极管和输出结电容,功率开关管的输出结电容和输出变压器的漏电感Lr作为谐振元件,使4个开关管依次在零电压下导通,实现恒频软开关。S1和S3构成超前臂,S2和S4构成滞后臂。为了防止桥臂直通短路,S1和S3,S2和S4之间人为地加入了死区时间△t,它是根据开通延时和关断不延时原则来设置同一桥臂死区时间。S1和S4,S2和S3之间的驱动信号存在移相角α,通过调节α角的大小,可调节输出电压的大小,实现稳压控制。Lf和Cf构成倒L型低通滤波电路。

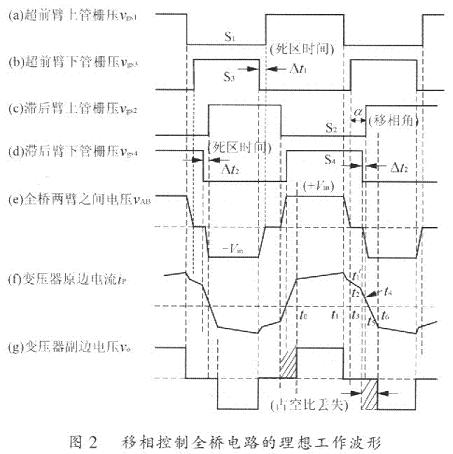

图2为全桥零电压开关PWM变换器在一个开关周期内4个主开关管的驱动信号、两桥臂中点电压VAB、变压器副边电压V0以及变压器原边下面对电路各工作模态进行分析,分析时时假设:

(1)所有功率开关管均为理想,忽视正向压降电压和开关时时间;

(2)4个开关管的输出结电容相等,即Ci=Cs,i=1,2,3,4,Cs为常数;

(3)忽略变压器绕组及线路中的寄生电阻;

(4)滤波电感足够大。

1.2 各工作模态分析

(1)原边电流正半周功率输出过程。在t0之前,Sl和S4已导通,在(t0一t1)内维持S1和S4导通,S2和S3截止。电容C2和C3被输入电源充电。变压器原边电压为Vin,功率由变压器原边传送到负载。在功率输出过程中,软开关移相控制全桥电路的工作状态和普通PWM硬开关电路相同。

(2)(t1一t1′):超前臂在死区时间内的谐振过程。加到S1上的驱动脉冲变为低电平,S1由导通变为截止。电容C1和C3迅速分别充放电,与等效电感(Lr+n2Lf)串联谐振,在谐振结束前(t2之前),使前臂中心电压快速降低到一0.7V,使D3立即导通,为S3的零电压导通作好准备。

(3)(t1′一t3):原边电流止半周箝位续流过程。S3在驱动脉冲变为高电平后实现了零电压导通,由于D3已提前提供了原边电流的左臂续流回路,虽然两臂中点电压为零,但原边电流仍按原方向继续流动,逐步衰减。

(4)(t3-t4):S4关断后滞后臂谐振过程,t3时加到S4的驱动脉冲电压变为低电平,S4由导通变为截止,原边电流失去主要通道。C4和C2开始充放电,与谐振电感Lr串联谐振。D2导通续流,为S2的零电压导通作好准备。原边电流以最大变化率从正峰值急速下降。

(5)(t4一t5):电感储能回送电网期。t4时刻D2已导通续流,下冲的电流经D2返回到电源EC,补偿了电网在全桥电路上的功耗。滞后臂死区时间应该在该时间段内结束。原边电流下冲到零点。

(6)(t5一t6):原边电流下冲过零后开始负向增大。S2和S3都已导通,形成新的电流回路,开始新的功率输出过程。但副边两整流二极管正是同时导通和急剧变换的过程,副边电压被箝位在低电平,出现占空比丢失过程。因此滞后臂死区时间设计是关键。

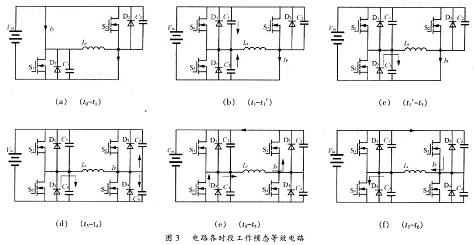

各时段工作模态等放电路如图3所示,图3中未画出变压器副边电路。

2 关键参数设计

2.1 死区时间设计

该变换器一个周期内有两个关键的死区时间,这两个死区时间的设计会影响到主开关管的电压应力限制和ZVS的实现。为了保证每个主开关管上电压应力为输入电压的一半,S1要比S3提早关断tdeadF1,S4要比S2提早关断tdead2。如果4个开关管的输出结电容COSS1~COSS4是一样的,从理论上讲只要tdead>0就可以了。但实际上4个开关管的输出结电容不可能完全一致,同时为了保证可靠,此区时间的设置应该满足如下的条件:S1上的电压到达Vin/2,也就是D1已经导通;同样,S4上的电压到达Vin/2,也就是D4已经导通,虽然4个开关管的输出结电容会有差异,但是在用上述方法设计时,可以把COSS1~COSS4看作是器件手册里给定的参数。假定都是COSS,要满足上述条件,死区时间的设计应满足如下不等式。

S2和S4的零电压是由激磁电感上的激磁电流在tdead2时间段对S3的结电容充电,同时埘S2和S4的结电容放电来实现的。实际上,死区时间不可能设计得很

- 改进型全桥移相ZVS-PWMDC/DC变换器(01-23)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)

- 移相控制ZVS PWM全桥变换器的直通问题分析(05-01)

- 10kW全桥移相ZVSPWM整流模块的设计(04-05)

- 基于改进型全桥电路的非隔离光伏并网逆变器(06-23)

- 液晶显示之殇(二)—电源篇(07-10)