应用于锁相环的脉宽调整电路的设计

前言

在锁相环PLL、DLL和时钟数据恢复电路CDR等电路的应用中,人们普遍要求输出时钟信号有50%的占空比,以便在时钟上升及下降沿都能够采样数据,最大限度地提高数据传输的速度。为了达到这一需求,我们经常需要在时钟的输出加入脉宽调整电路来得到一个占空比尽可能达到50%的时钟信号。

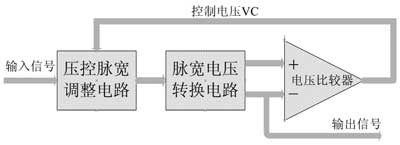

近年来诞生了许多种类的脉宽调整电路。这些电路大致可以分为以下三类:第一类最为简单,即采用2分频器产生占空比为50%的时钟,2分频器并不是专为调整占空比而采用的,但的确达到了这一需求;第二类通过负反馈机制,采用数字或模拟控制,调整信号占空比,这类电路最主要考虑的是系统稳定性;最后一种是采用复杂数字算法的占空比调整电路,其实现相对比较复杂。因此本文主要分析设计前两种类型的脉宽调整电路。

2分频器作为脉宽调整电路

绝大多数PLL中使用2分频prescaler电路处理VCO输出的高频信号,既实现了反馈路径上的预分频要求,降低了后续反馈分频电路的工作频率和功耗;又实现了对输出信号脉宽的调整,基本满足了50%占空比的要求。但其最大的缺点在于减少了压控振荡器VCO一半的输出信号范围,对于高频信号的50%占空比需求,这一缺点体现得比较明显。

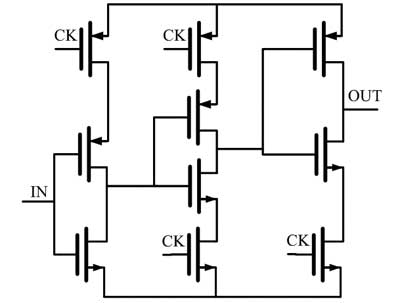

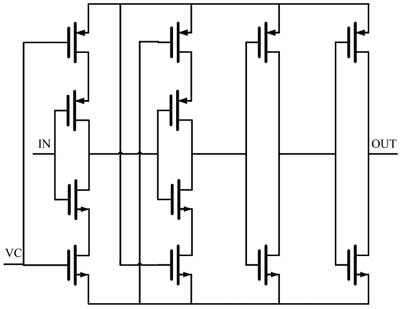

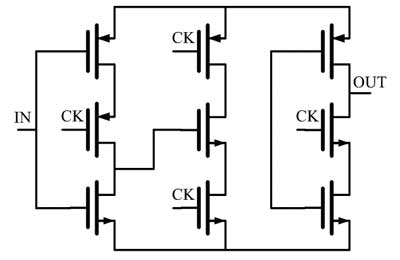

通常我们采用静态D触发器实现2分频,为了实现在高频工作时降低功耗,现在越来越多采用动态逻辑电路实现2分频。图1是一种传统的九管实现的动态2分频器。当时钟¢为低电平时,第一级时钟开关导通,采样输入信号,这时第二级输出的高电平保证了该电路的即时输出是前一次采样保持得到的信号,该信号电荷储存于输出节点的寄生电容。由于现代CMOS工艺已经进入深亚微米阶段,晶体管的漏电流现象越发明显,因此,该电路正常工作的频率不能太低。当¢变为高电平后,第一级刚才所采样的信号正确到达第三级的输入端,¢的高电平使得这一级成为普通反相器,实现了触发器的功能。由于采用了动态机制,利用寄生电容采样保持信号,减少了直流通路,降低了功耗,与静态逻辑实现方法相比,所用晶体管数量大大减少。该电路设计中,主要考虑时钟MOS开关的导通电阻和开关速度的折中以及信号上升下降时间的大致匹配。为提高该电路的速度,可以按照图2所示改进,与图1电路相比,时钟MOS开关更靠近电地,因此速度更快。对图2电路仿真结果表明,该电路最高工作频率可以达到12GHz。

图1 传统的动态触发器

|

- 全数字锁相环的设计及分析(03-01)

- 一种大电压输出摆幅低电流失配电荷泵的设计(04-22)

- 锁相环同步检波技术及在视频检波中的应用(05-20)

- 一种基于CMOS工艺的电荷泵锁相环芯片的设计(05-21)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环相位噪声与环路带宽的关系分析(08-04)