基于Nios II的数字音频录放系统的设计

时间:01-08

来源:21IC

点击:

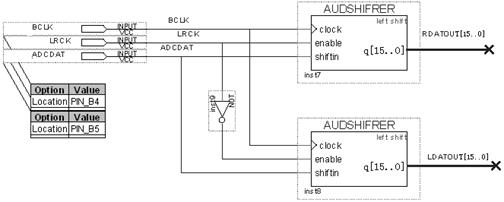

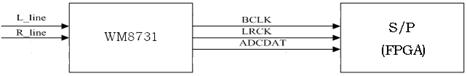

图2 主模式的WM8731与串/并转换模块的连接图 本设计中,串并转换模块由两个16位的移位寄存器构成,分别对左声道和右声道的位数据流进行串/并转换,电路构成如图3所示。两个移位寄存器inst7和inst8由LRCK和LRCK的非信号使能,当LRCK为低电平时,移位寄存器inst8工作,对左声道的数据流进行串并转换,当LRCK为高电平时,移位寄存器inst7工作,对右声道的数据流进行串并转换。

|

SOPC EDA I O接口 硬件协处理器 处理器 相关文章:

- 基于SOPC技术的交通事故自动处理设备(10-05)

- 边缘图像连通区域标记的算法研究和SoPC实现(06-13)

- SOPC设计中自定义IP的开发(02-18)

- 基于SOPC技术的软件无线电系统研究(04-07)

- AGC中频放大器设计(上)(10-07)

- 第三方IP:SoC设计的一种不稳固基础(09-15)