SOPC设计中自定义IP的开发

1 SOPC技术与IP核

SOPC的主要思想是提供一个IP库,用户从IP库中选择IP核来组装系统,因此IP核是SOPC设计的关键技术之一。虽然IP核一词在众多场合被使用,但它并没有一个统一的定义。从概念上可以这样理解它:IP核是指将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、UART控制器等设计成可修改参数的模块,让其他用户可以直接调用这些模块,这样就大大减轻了工程师的负担,避免重复劳动,缩短系统开发时间。IP 核设计一般可以有3个来源:EDA厂商提供,用户自己定义,第三方提供。

IP核可以分为3类:

(1) 软核(soft-core)。软核用硬件描述语言写成,可以是对设计的算法级描述,或功能级描述,也可以是仅仅用于功能仿真的行为模拟。

(2) 固核(firm-core)。固核在软核基础上开发,是一种可综合的、并带时序信息及布局布线规划的设计,用硬件描述语言写成。

(3) 硬核(hard-core)。指和特定工艺相联系的物理版图,设计的正确性已经投片验证, 可在新设计中作为特定的功能模块直接调用。

一般来说,EDA厂商及第三方提供的IP核都是功能上比较通用的,但在进行SOC设计时,用户经常有特殊需求,这时必须自定义逻辑来实现所要的功能。所以在进行SOC设计时,如何灵活地加入用户自定义逻辑就显得尤为重要。

2 基于EDK的SOPC开发技术

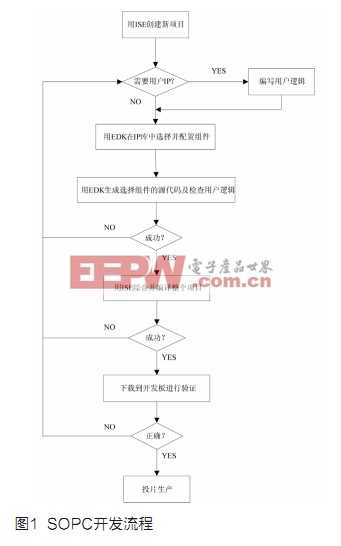

进行SOPC系统开发,首先是要选择的是FPGA平台、处理器方案以及开发软件,目前常采用的是由世界上两大主要的FPGA器件生产厂商所提供的平台、SOPC方案及相关开发套件:一是Altera公司的FPGA产品,采用Nios处理器软核或硬核ARM,开发工具由QuartusⅡ和SOPC Builder组成;二是采用Xilinx公司的FPGA,基于Microblaze软核或Powerpc405硬核,开发工具由ISE和EDK组成。下面就以Xilinx公司的软件EDK为例介绍SOPC系统的开发过程。EDK有一个友好的图形用户界面,通过这个界面,用户可以从Xilinx提供的IP库中选取一些组件,如处理器、SDRAM、Flash、各种I/O等,并可通过选择配置相应的参数。EDK有个尤为重要的功能:在进行SOPC设计时,如果用户有特殊功能要求,但IP库中没有,则用户可以加入自定义的逻辑来实现,具体的流程如图1所示。

这里以一个在控制系统中常用的脉冲宽度调制电路(PWM)为实例,设计一个PWM用户逻辑并利用EDK将它集成SOPC系统中。我们事先假定FPGA中已经存在一个基于Microblaze的嵌入式系统,在此前提下将PWM外设集成到OPB总线上,并进行功能验证。

假设PWM的具体设计要求如下:

◇ 要求信号周期可调。

◇ 脉冲的宽度可调。

◇ 可以控制PWM的输出使能。

◇ PWM直接通过一个FPGA管脚输出。

按照以上设计要求,我们设定PWM外设共有3个寄存器,分别为:

(1) Clock_Divisor 决定信号周期的32位寄存器

(2) Duty_Cycle 控制信号占空比的32位寄存器

(3) Control 控制寄存器,使能输出,32位,只有最低位有效

3.1 模块功能设计

PWM外设的核心是一个计数器,由Clock_Divisor控制计数周期,当计数器的计数值大于Clock_Divisor寄存器的值时,计数器清零,否则在时钟信号触发下,输出使能控制位为1时计数器加1计数;PWM模块的输出是计数器的计数值与Duty_Cycle比较的结果,当输出使能有效并且计数值大于Duty_Cycle寄存器的值时,输出为1,否则输出为零。

3.2 模块集成

在XPS集成开发环境中,集成了一个creat/import peripheral wizard 工具,利用该向导工具就能轻松地创建或导入一个用户自定义的外设。在向导中我们只需选择与总线的接口是3个32位的寄存器即可,向导完成后,工程目录(project)中会自动生成drivers和pcores两个文件夹,两个文件夹中包含了自定义外设的相关信息,drivers文件夹里以应用程序接口函数(API)的形式提供了自定义外设的驱动程序,以完成对外设的读写和测试, 用户在开发包含自定义外设的高层应用软件时就可以直接调用这些接口函数。

在pcores文件夹底下有三个文件比较重要:user_logic、MPD和PAO文件,user_logic文件是集成工具生成的用户模板文件,该文件中给出了自定义逻辑与OPB总线的接口信号,用户只需根据接口信号的驱动要求,在用户模板中就能完成模块的功能设计。PWM外设与总线的接口描述如下:

entity user_logic is

generic

( 总线协议参数设置,不允许用户修改

C_AWIDTH : integer := 32;

C_DWIDTH : integer := 32;

C_NUM_CS : integer := 1;

C_NUM_CE : integer := 3

);

port

(

pwm_out : out std_logic; --这是PWM模块的输出端口

-- 以下是总线接口信号,不允许用户修改或删除,否则模块集成时将会出错

Bus2IP_Clk : in std_logic;

Bus2IP_Reset : in std_logic;

Bus2IP_Addr : in std_logic_vector(0 to C_AWIDTH-1);

Bus2IP_Data : in std_logic_vector(0 to C_DWIDTH-1);

Bus2IP_BE : in std_logic_vector(0 to C_DWIDTH/8-1);

Bus2IP_CS : in std_logic_vector(0 to C_NUM_CS-1);

Bus2IP_RdCE : in std_logic_vector(0 to C_NUM_CE-1);

Bus2IP_WrCE : in std_logic_vector(0 to C_NUM_CE-1);

IP2Bus_Data : out std_logic_vector(0 to C_DWIDTH-1);

IP2Bus_Ack : out std_logic;

IP2Bus_Retry : out std_logic;

IP2Bus_Error : out std_logic;

IP2Bus_ToutSup : out std_logic

);

end entity user_logic;

其中Bus2IP_WrCE是处理器用来对外设的寄存器进行编址的信号,该信号与寄存器地址映射关系如表1所示。

- 基于Nios II的数字音频录放系统的设计(01-08)

- 基于SOPC技术的交通事故自动处理设备(10-05)

- 边缘图像连通区域标记的算法研究和SoPC实现(06-13)

- 基于SOPC技术的软件无线电系统研究(04-07)

- 基于SOPC的雷达多功能接口模块的设计与实现(06-24)

- 基于电流极限比较器的设计(11-24)