基于SOPC技术的软件无线电系统研究

在软件无线电的早期实现方案中多是用DSP和ASIC来完成。然而这种方案有2个突出的缺点:一是系统的速度很难满足高速动态实时数字信号处理的要求;二是系统的体积大、功耗高。这2个突出缺点制约了软件无线电的推广和应用。随着可编程逻辑器件密度、规模和速度的快速增长,各个可编程逻辑器件厂商开始提出自己的SOPC片上可编程系统的软件和硬件一体化解决方案,为实现高速数字信号处理提供了可能。本文运用基于FPGA的SOPC技术构建了软件无线电平台,极大地提高了数字信号处理的能力和速度,减少了系统的功耗和体积。

1 软件无线电的结构

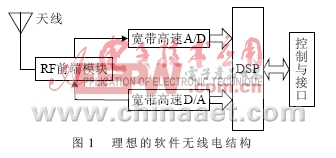

软件无线电的核心思想是将A/D、D/A尽可能地靠近天线,减少模拟处理的环节。在接收端:由天线接收的无线电信号经过必要的低噪声放大后,就直接对其进行数字化(ADC),数字化后的信号经过DSP完成数字下变频、数字滤波、数字解调等信号处理任务;在发射端:需要发射的基带信号通过DSP完成数字调制、数字上变频和数字滤波等信号处理任务后,经DAC转变为模拟信号,然后通过功率放大器放大到足够功率,最后由天线发射出去。理想的软件无线电结构如图1所示。

实际上,上述的软件无线电结构是很难实现的。首先,根据奈奎斯特采样定理,A/D的采样速率至少是其工作带宽的2倍。例如:对于工作在2 MHz~2 000 MHz的JTRS电台,其采样频率至少要达到4 GHz。目前A/D器件的采样频率很难达到这个要求,而且,如果A/D采样后的大量数据流直接交由DSP处理,将给DSP带来巨大的运算压力。以A/D采样速率仅为100 MHz的A/D器件为例,DSP每处理1个采样信号,大约需要100次运算,则总的运算速率为100×100 M=104 MIPS。这样高的运算速率,目前的DSP芯片还难以达到。

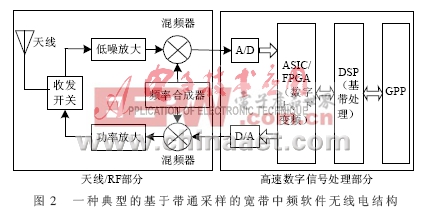

针对上述问题,目前最常用的一种解决方案为:基于带通采样的宽带中频软件无线电结构。它的主要思想是:把射频信号通过混频搬移到中频再带通采样,使得A/D采样率、输入带宽满足系统要求,同时在DSP前加数字下变频器。

中频带通采样软件无线电结构采用多次混频体制,即超外差体制,把工作频段上的某一感兴趣的宽带射频信号经过放大、混频和滤波变换到统一的中频FIF上,最后由A/D转换器对中频信号进行采样数字化。它的最大好处就是降低了对A/D采样速率的要求,使软件无线电可实现性更强,但是也使得射频前端复杂化。

限于目前DSP的处理瓶颈,A/D采样后的大量数据一般先交由数字下变频器进行一些前期的处理再传递给DSP进行处理。数字下变频器一方面从包含所有信道的宽带信号中分离出某一用户窄带信道,另一方面对分离出的某一用户通道信号抽取、滤波和降低数据速率。数字下变频器可采用专用的ASIC芯片,如TI公司生产的GC5016芯片等,也可采用FPGA编程来实现。与专用的数字下变频器件相比,FPGA具有更大的灵活性,不会过分依赖于硬件,只需对软件进行修改就可以对系统进行升级和维护。

图2所示为一种典型的带通采样的宽带中频软件无线电结构。该设计方案中DSP主要完成基带信号处理(如定时同步、信道估计、FFT变换、解交织、编译码等)。通用微处理器GPP(General Purpose Processor)一般使用实时操作系统RTOS(Real Time Operation System)来进行任务调度和存储器管理。

2 软件无线电的解决方案

本文主要实现图2中的高速数字信号处理部分,数字信号处理模块是软件无线电的核心部分。在图2中的是高速数字信号处理部分的一种常用方案,通常是采用分离部件搭建的系统存在体积大、功耗高、成本高、各个单元之间的数据传输速率受限等缺点。SOPC方案可解决以上问题,并且还具有极高的灵活性和可扩展性。

SOPC技术是美国Altrea公司于2000年最早提出的。SOPC是一种特殊的嵌入式系统:首先,它是系统芯片(SOC),即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,具有灵活的设计方式,可裁剪、可升级、可扩充,并具备软硬件在系统可编程的功能。它结合了SOC和FPGA的优点,具有以下基本特征:至少包含1个以上的嵌入式处理器IP核;具有小容量片内高速RAM资源;丰富的IP核资源可供灵活选择;有足够的片上可编程逻辑资源;处理器调试接口和FPGA编程接口共用或并存;可包含部分可编程模拟电路;单芯片、低功耗[3]。

目前主要的嵌入式处理器IP核有软核和硬核2种,本文采用Altera公司的Nios II软核处理器。Nios II核是用户可随意配置和构建的32位总线指令集和数据通道的嵌入式微处理器IP核,采用Avalon总线结构通信接口。Nios II有3种性能的处理器内核可供选择:快速的内核(Nios II/f)提供高性能;经济的内核(Nios II/e)满足低成本;标准的内核(Nios II/s)则用于性能和尺寸的平衡。此外,Nios II核含有许多可配置的接口模块核,包括:可配置高速缓存(包括片内ESB、外部SRAM或SDRAM)模块、可配置RS232通信口、SDRAM控制器、标准以太网协议接口、DMA、定时器、协处理器等。在下载进FPGA前,用户可根据设计要求,利用Quartus II和SOPC Builder,对Nios II及其外围系统进行构建,使该嵌入式系统在硬件结构、功能特点、资源占用等方面全面满足用户系统设计的要求。Nios II核在同一FPGA中被植入的数量没有限制,只要FPGA的资源允许[4]。

采用SOPC技术对图2中的高速数字信号处理部分进行改进,设计的SOPC方案如下:将原来由ASIC、DSP和GPP完成的工作全部交由1片FPGA构成的SOPC系统来完成。本文介绍了一种基于SOPC技术的软件无线电系统解决方案,如图3所示。

- 基于Nios II的数字音频录放系统的设计(01-08)

- 基于SOPC技术的交通事故自动处理设备(10-05)

- 边缘图像连通区域标记的算法研究和SoPC实现(06-13)

- SOPC设计中自定义IP的开发(02-18)

- 对热电制冷的营养液温控系统研究2(10-10)

- 对热电制冷的营养液温控系统研究(10-10)