跨越鸿沟:同步世界中的异步信号

时间:08-21

来源:Mike Stein,Paradigm Works

点击:

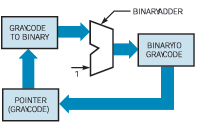

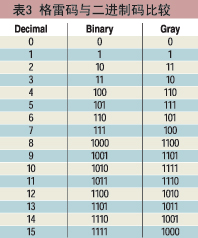

表 3 格雷码计数器是一个二进制累加器,在累加器前、后各带有一个转换器,分别用于格雷码转换为二进制码,和二进制码转换为格雷码(图 8)。格雷码与二进制码的转换是一个异或运算,所以只需比一个二进制计数器多几个逻辑电平。在格雷码转换成二进制码时,使用:BN=GN;BN-1=BN+GN-1;BN-2=BN-1+GN-2 . B1=B2+G1;B0=B1+G0。而将二进制码转换成格雷码时,使用:GN=BN;GN-1=BN+BN-1;GN-2=BN-1+BN-2 . G1=B2+B1;G0=B1+B0。在设计中可以采用同样的技术来比较格雷码指针的值,即在各个指针与二进制比较逻辑之间增加转换器。

|

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)