跨越鸿沟:同步世界中的异步信号

时间:08-21

来源:Mike Stein,Paradigm Works

点击:

一个触发器中。

一个经同步后的信号在两个时钟沿以后就成为新时钟域中的有效信号。信号的延迟是新时钟域中的一到两个时钟周期。一种粗略的估算方法是同步器电路在新时钟域中造成两个时钟周期的延迟,设计者需要考虑同步延迟将对跨时钟域的信号时序造成的影响。

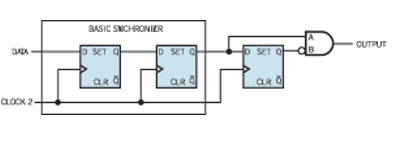

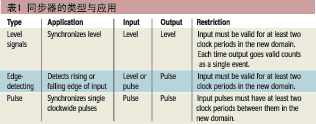

同步器有许多种设计方法,因为一种同步器不能满足所有应用的需求。同步器的类型基本上有三种:电平、边沿检测和脉冲(表 1)。虽然还存在着其它类型的同步器,但这三种类型的同步器可以解决设计者遇到的多数应用问题。在电平同步器中,跨时钟域的信号在新时钟域中要保持高电平或低电平两个时钟周期以上。这种电路的要求是,在再次成为有效信号前,信号需要先变成无效状态。每一次信号有效时,接收逻辑都会把它看作一个单个事件,而不管信号的有效状态保持了多久。这种电路是所有同步器电路的核心。

一个经同步后的信号在两个时钟沿以后就成为新时钟域中的有效信号。信号的延迟是新时钟域中的一到两个时钟周期。一种粗略的估算方法是同步器电路在新时钟域中造成两个时钟周期的延迟,设计者需要考虑同步延迟将对跨时钟域的信号时序造成的影响。

同步器有许多种设计方法,因为一种同步器不能满足所有应用的需求。同步器的类型基本上有三种:电平、边沿检测和脉冲(表 1)。虽然还存在着其它类型的同步器,但这三种类型的同步器可以解决设计者遇到的多数应用问题。在电平同步器中,跨时钟域的信号在新时钟域中要保持高电平或低电平两个时钟周期以上。这种电路的要求是,在再次成为有效信号前,信号需要先变成无效状态。每一次信号有效时,接收逻辑都会把它看作一个单个事件,而不管信号的有效状态保持了多久。这种电路是所有同步器电路的核心。

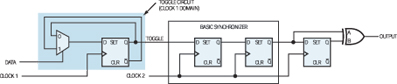

表 1 边沿检测同步器在电平同步器的输出端增加了一个触发器(图 2)。新增触发器的输出经反相后和电平同步器的输出进行与操作。这一电路会检测同步器输入的上升沿,产生一个与时钟周期等宽、高电平有效的脉冲。如果将与门的两个输入端交换使用,就可以构成一个检测输入信号下降沿的同步器。将与门改为与非门可以构建一个产生低电平有效脉冲的电路。

|

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)