基于FPGA 的谐波电压源离散域建模与仿真

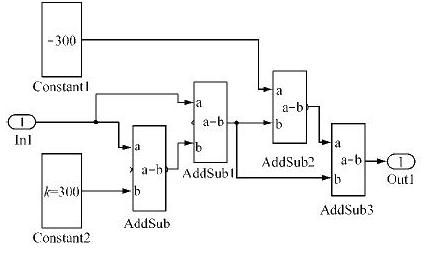

法器运算结果为负时,输出为0;运算结果为正时,输出为正常值。Constant1 和Constant2分别设置限幅模块的上、下限,限幅环节的模型如图5 所示。

图5 限幅环节模型。

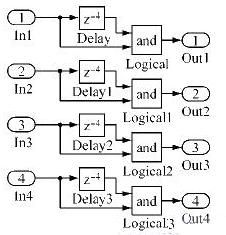

利用延迟模块和逻辑模块,可设置逆变器死区时间。输入信号经过Delay 模块,被延迟4 个采样周期时间,再与原信号进行逻辑与运算,就可得到带有死区时间的PWM 信号,被Delay 模块延迟的时间就是设置的死区时间。死区时间模型如图6 所示。

图6 死区时间的VHS-ADC 模型

依靠平台提供的co-simulink 接口,将搭建的离散域控制模型进行编译,并自动生成代码,下载到FPGA,生成一个bit 流文件,将含有bit 文件的协议同仿真模块与谐波电压源的主电路连接。当在Simulink 中进行仿真时,FPGA 上的实时运算结果返回到Simulink 环境中,提高了仿真速度。

3 仿真结果

利用Matlab /Simulink 软件和VHS-ADC 仿真平台,建立完整的谐波电压源仿真模型。仿真参数:输入电压为Uu = Uv = Uw = 220 V;滤波电感L = 0. 05 mH,滤波电容C = 100 μF。电压环PI 参数:比例系数Kp = 13,Ki = 0. 4;电流环PI 参数:比例系数Kp = 15,Ki = 0. 2,负载R = 30 Ω;采样时间为100 ns,单相额定输出功率为3 kVA。

稳态下,谐波电压源输出的单相基波波形如图7 所示。因为三相不可控整流提供的直流电压需要约0. 01 s 才能达到稳定,所以谐波电压源输出波形在0. 01 s 之前是逐渐增大的,当直流电压稳定后,仿真波形几乎与期望波形重合。

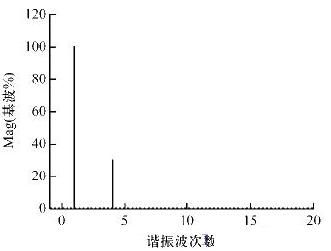

为了验证装置的谐波合成能力,将30 V 4 次谐波叠加到100 V 基波上,如图8 所示。叠加后的波形在0. 01 s 前逐渐增大,在0. 01 s 后几乎与期望波形重叠;将所得波形进行傅里叶分析,4 次谐波含量为基波的30%,其频谱分析图如图9 所示。

图7 基波输出波形与期望波形的对比。

图8 叠加信号输出波形与期望波形的对比。

图9 叠加波形的频谱图。

表1 为输出波形为单次谐波时,总谐波畸变率(THD)的大小。仿真结果表明,谐波电压源输出21 次内的单次谐波时,其THD 不会超过1%。

上述仿真结果说明了谐波电压源输出波形具有很高的精度,同时也验证了谐波电压源离散域模型的正确性。

表1 谐波电压源输出单次谐波时的畸变率。

4 结语

分析了谐波电压源的主电路模型,探讨了基于滤波电容电流和负载电压瞬时值的双闭环PI控制策略,利用VHS-ADC 数字信号处理系统采样率高、实时性强、建模灵活等特点,构建离散域实时仿真控制模型。仿真结果表明,该设计方法和离散化模型是正确的,说明了基于FPGA 进行谐波电压源研究的可行性。

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)

- Xilinx Virtex UltraScale 开发平台(06-12)