一款用DSP+FPGA实现的数字相关器

,用于存放处理过程所需要的数据及中间结果。FLASH ROM 中存储了DSP 执行程序和FPGA 的配置数据。先进先出( FIFO) 器件则用于实现信号处理中常用到的一些操作,如延迟线、顺序存储等。

在本系统的设计中,DSP 采用TI 公司的C5409A ,同时采用SPANSION 公司的AM29LV200BT 作为DSP 的外挂FLASH ,存放相应的程序; FPGA 采用的是Xilinx 公司的XCV600E ,同时采用Xilinx 公司的XC18V00 作为专用配置芯片,存放FPGA 程序;在FPGA 中将进行FIFO 的设计,DSP 通过对FIFO 的读取来实现两块芯片间的通信。

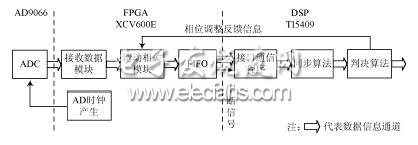

总体的算法分为FPGA 和DSP 部分: FPGA 的算法主要包含的功能是,产生AD 采样时钟,接收AD 数据,滑动相关,FIFO 构成及DSP 中断产生;DSP 含有:同步算法,判决算法。

以下是算法在各芯片中的嵌入分配示意图,如图3所示。

图3 算法在各芯片中的嵌入示意图

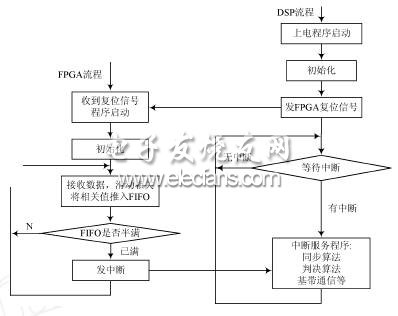

FPGA 和DSP 两部分的算法必须协同运行,他们之间的关系是:FPGA 的算法由时钟来驱动,每个时钟到来时,他都要进行相应的数据接收,滑动相关,将相关值推入FIFO 的操作,当他将FIFO 置到一定程度时,则向DSP 发中断信号;DSP 的程序在大部分时间处于一种循环等待的状态,而他一收到FPGA 的中断,则进行响应,先将FIFO 里面的若干数据读出,然后进行相应的中断处理,由DSP 完成同步处理,相关判决并实现基带通信。总的流程图如图4 所示。

系统的运行的实测性能

正常通信时,误码率稳定在1*10-5 。高斯噪声干扰(未解扩解调前加干扰) ,语音信号正常通信(误码率≤1×10-3 ) 的信干比:-17dB。在抗干扰方面,对于非瞄准式单频干扰语音信号的正常通信(误码率≤1×10-3 ) 的信干比:-14~-2dB(随频点有差异) ;而对于瞄准式单频干扰当达到- 12 dB 时,仍能继续保持语音通信。

图4 FPGA 及DSP 流程图

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)