DSP串行通信在减摇水舱试验台架控制系统中的应用

TMS320LF2407是美国TI(Texas Instruments)公司专为数字伺服控制和嵌入式控制系统而推出的一种低功耗、高性能16位定点DSP芯片。通过把高速的数字信号处理器内核和功能强大的片内外设集成在一起, DSP成为传统的微控制单元和多片设计系统的一种理想替代品。

在减摇水舱&search=1" target="_blank">减摇水舱试验台架控制系统工作过程中,需要实时修改DSP中控制器参数等变量,因此如何实现PC机与DSP的可靠通信成为一个重要问题。串行通信具有连接简单、使用灵活方便、数据传递可靠等优点,在工业监控、数据采集和实时控制系统中得到了广泛应用。因而,本系统中采用了串行通信进行参数传送。

本文基于减摇水舱试验台架控制系统,设计了一种实现DSP与PC机串行通信的方案。

2 减摇水舱试验台架控制系统

减摇水舱是减小船舶横向摇摆的重要减摇装置之一,对减摇水舱除了进行理论研究外,建立减摇水舱的试验装置是对减摇水舱进行研究的重要手段。减摇水舱试验台架是研究和设计减摇水舱的重要试验设备,它可以模拟实际舰船在海浪中的运动,研究水舱的运动、控制规律,并可测得其减摇效果。

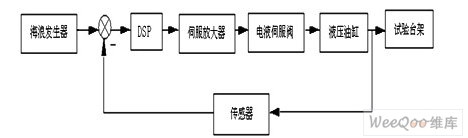

为了使水舱试验台架能够模拟实船在海浪中的运动并研究水舱的实际作用效果,必须有一套能够模拟海浪横摇力矩的力矩伺服系统。由于海浪横摇力矩幅值和频率变化很快,对力矩伺服系统的要求较高,所以试验台架采用电液力矩伺服系统。减摇水舱试验台架系统如图1所示。

图1 减摇水舱试验台架系统框图

在减摇水舱试验台架控制系统中,采用PC机和DSP的主从式结构。PC机作为上位机,提供海浪横摇力矩信号、对一些传感器采集得到的数据进行显示,而DSP作为下位机,完成对减摇水舱试验台架电液伺服系统的实时控制。其输出电压信号经伺服放大器控制流量电液伺服阀,由伺服阀控制摆动油缸,由液压油缸驱动试验台架系统,摆动油缸输出的海浪横摇力矩由传感器检测送至DSP构成闭环控制回路。

3 TMS320LF2407及串行通信接口&search=1" target="_blank">串行通信接口(SCI)

3.1 TMS320LF2407简介

TMS320LF2407除了具有TMS320系列DSP的基本功能,还具有一些适合应用于数字伺服控制的特点。采用高性能静态CMOS技术,使得供电电压为3.3V,降低了控制器的功耗,而且高达40MIPS的执行速度使指令周期缩短到25ns,提高了控制器的实时控制能力。TMS320LF2407片内有高达32K 16位的Flash程序存储器,544字的双端口RAM(DARAM)和2K字的单口RAM(SARAM)。TMS320LF2407的片内外设非常丰富,包括两个事件管理器模块、10位A/D转换模块、看门狗定时器、CAN现场总线接口、基于锁相环(PLL)的时钟发生器、PWM信号通道、串行外设接口(SPI)、串行通信接口(SCI)。TMS320LF2407提供的片内外设资源使得数字伺服控制应用中所需使用的外围芯片大大减少了,为应用系统的设计提供了方便

3.2 串行通信接口(SCI)

串行通信模块的寄存器是8位的,并且可编程。串行通信接口(SCI)支持DSP和其他使用标准NRZ(非归零)格式的异步外设之间的异步串行数字通信。SCI模块会对接收到的数据进行测试,如间断测试、奇偶性、超时以及帧错误测试等,以确保数据的完整性。可编程1-8位数据长度和1-2位停止位。SCI模块有双缓冲的发送器和接收器,每个都有独立的使能位和中断位,两者可独立工作,也可同时在全双工模式下工作,并且发送和接收操作均可通过中断和查询两种方式来进行。在该模块中,通过对一个16位波特率选择寄存器编程,可获得超过65000种不同的波特率。

在TMS320LF2407与其他异步外设的串行通信中,对SCI模块的控制、波特率和字符格式的选择、操作方式和通信协议的选择、中断优先级的选择和使能等都是通过对相关寄存器编程来实现的。

4 本系统中串行通信设计方法及协议

SCI有两种多处理器协议,即空闲线多处理器模式和地址线多处理器模式。这些协议允许在多个处理器之间进行有效的数据传输。在本系统中,采用空闲线模式。在此模式下,当接收到数据块起始信号后,串行通信接口被唤醒。处理器识别下一个串行通信接口中断。中断服务程序将接收到的地址与自己的地址进行比较。如果该CPU正在被寻址,则中断服务程序清除SLEEP位,并接收数据块中剩余的数据。如果该CPU不被寻址,则SLEEP位仍保持置位。这样就允许CPU继续执行它的主程序而不被SCI所中断,直到检测到下一个块的起始信号。

DSP接收和发送数据可以采用查询或中断两种模式来实现。本系统中采用中断方式来接收PC机所传来的参数,这里主要介绍该模式下数据接收和发送的具体方法。TMS320LF24

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)