一款用DSP+FPGA实现的数字相关器

数字相关器作为软件无线电的典型应用,在扩频通信中成为必不可少的技术。在传统的扩频通信中,采用模拟器件(如:声表面波器) 来实现解扩单元,而用数字相关器可以增加系统的灵活性和稳定性,因此,对数字相关器的研究具有较大的意义。本文采用DSP+FPGA 的结构,一方面使设计更加灵活,同时也降低了生产的代价。从通用性上考虑,本文采用零中频的采样系统。提出接收端如何正确地把信道中的模拟信号通过正确的零中频采样及数字相关器后恢复成数字信号。本文给出了数字相关的算法及仿真结果,用DSP+FPGA 实现的算法流程图,最后给出了系统的实测结果。

解扩算法简介

发端的信号模型

对于数字信号,将其分别投影到I ,Q 两路正交信号,其特征相同,因此这里仅对I 路信号进行分析,同理可得出Q 路信号。

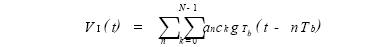

I 路基带信息经信道编码后,速率为3.103 kb/s ,码元间隔为323 μs , 然后进行PN 码扩频, PN 码的长度为1 023 ,速率为3.174 Mcps ,因此,扩频后I 路基带码片的速上升为3.174 Mcps ,扩频增益为30 dB。信号可表示为:

其中an=±1 ,n ∈(0 ,∞) 为信息码, ck 为扩频码, gTb (t) 为矩形脉冲, Tb = 310 ns (此处未考虑脉冲成型,通常应采用升余弦脉冲) 。

相关峰捕获及同步判决算法分析及数学推导

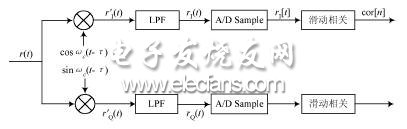

在收端,先对收到的QPSK 信号进行解调,解调采用相干解调的方式,首先对模拟基带波形采样,对得到的数据流进行滑动相关,得到一个相关值。由于PN 码的固有特性,当本地PN 码与数据流中的相关码对齐时(同步) ,便可得到很高的相关峰,而没有对齐时(未同步) ,得到的相关值很小,这种特性一方面降低了系统误判的可能性,另一方面也提高了系统的抗干扰性能。解调解扩的相应框图如图1 所示。

图1 收端解扩解调模型

假设信道是高斯白噪声信道,只存在时延,高斯白噪声,没有多径扩展,则收到的信号r( t) 与发端的信号s( t)存在以下的关系:

此处,τ为信道传播时延, n( t) 为信道噪声。经过本地载波相乘后,可得r′I ( t) 表达式如下:

由于本地载波是接收到的信号经过锁相环提取的,故信道时延带来的载波时延也能被捕获,故用cos ωc( t - τ)来表示本地载波。

r′I ( t) 经过一低通滤波器, 得到r I ( t) , 为讨论方便,假设低通滤波器能滤除二倍频分量,同时通带内的相应为常数2 。

由此可见,在理想情况下,可将发端I 路的信号得到恢复,事实上已经完成了解调任务。接下来就是AD 采样,在这里把AD 采样的速率设定为切普码率的4 倍,相当于在做相关时,有4 路信号可供计算,这样做的好处是每次优选最好的一路,提高接收性能。事实上,采样率越高对于性能的提高越有好处,但是不能无限度地提高,因为后端的数字器件有一个处理能力的限制。由于4 路采样信号在数字解扩模块的处理是相互独立的,所以这里只对一路采样信号进行研究。由于只对一路信号进行研究,所以采样率Ts 可等效为切普速率, 本系统中Ts =1/3.1M。

特点,互相关值很小。由上式可见,第二项是影响误判的主要因素,此处对于误码率的讨论不同于一般意义的QPSK+扩频方式,因此将采用仿真的方式对误码率进行讨论。[next]

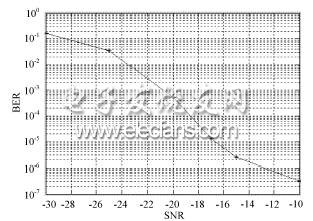

利用计算机仿真,可得到高斯噪声下的误码率曲线如图2 所示。从仿真结果看,当SNR ≥- 20 dB 时,满足语音通信(BER ≤10-3 ) 的要求;当SNR ≥- 14 dB 时,满足数据通信(BER ≤10-6 ) 的要求。

图2 高斯信道的误码性能

算法在DSP+FPGA 系统中的实现

由于数字相关模块主要由FPGA 和DSP 来完成,因此主要的算法将嵌入进这两个芯片中。

DSP+FPGA 系统的最大优点是结构灵活,有较强的通用性,适合于模块化设计,从而能够提高算法效率;同时其开发周期较短,系统容易维护和扩展,适合实时信号处理。

实时信号处理系统中,低层的信号预处理的数据量大,对处理速度的要求高,但运算结构相对比较简单,适用于FPGA 执行硬件实现,这样能同时兼顾速度和灵活性。高层处理算法的特点是所处理的数据量较低层算法少,但算法的控制结构复杂,适用于运算速度高、寻址方式灵活、选用通信机制强大的DSP 芯片来实现。

DSP+FPGA 系统的核心由DSP 芯片和可重构器件FPGA 组成。另外还包括一些外围的辅助电路,如存储器、先进先出( FIFO) 器件及FLASH ROM 等。FPGA 电路与DSP 相连,利用DSP 处理器强大的I/O 功能实现系统内部的通信。从DSP 角度看,FPGA 相当于他的宏功能协处理器。外围电路辅助核心电路进行工作。DSP 和FPGA 各自带有RAM

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)