基于DM642的视频处理系统硬件设计

近年来,视频处理系统的研究受到了人们越来越多的关注,发展也非常迅速。同时,视频技术也是一门跨越很多学科的技术,在此基础上又衍生出了很多的新的技术和研究方向,比如人脸识别技术和图像边缘检测算法的研究以及视频压缩算法的研究等。现在视频处理系统有着广泛的应用,比如交通路口的监控装置、在机场、港口以及一些公共场所使用的视频监控设备等。如果视频技术再和图像处理等技术结合起来,那么其应用的范围和深度都会有很大的提高,比如在安防领域可以用于辅助识别危险目标和恐怖分子等,这些技术在民用领域和军事领域都有着广泛的应用。

针对以上这些应用需求,本文采用TI公司的TMS320DM642(以下简称DM642)数字多媒体处理芯片设计了一套视频处理系统。文中主要介绍了系统的硬件设计和调试过程。

1 系统硬件设计方案

1.1 系统的硬件结构

视频处理系统的硬件设计采用的DSP是DM642,它是一款高性能的数字多媒体处理器,最高运算速度可达5760MIPS(每秒百万条指令),可以满足复杂算法的实时处理要求。视频信号需要通过CCD摄像头采集。

视频解码芯片将采集到的模拟信号转换为数字信号供DSP进行运算处理。DM642的视频接口(VP口)共有3个,其中VP0和VP1都是20位,10位用于视频输入,另外10位用于音频输入。VP2口也是20位,可以分为两路视频输入。在本文设计的视频处理系统中,采集到的模拟视频信号经过视频解码芯片模/数转换后,形成BT.656格式的数字视频信号,通过DM642的VP0口输入。

数字信号经过DM642的软件编码器进行编码压缩处理,编码压缩生成的视频码流数据打包后通过RJ-45接口经以太网传送到远端的上位机,上位机作为SERVER,这样就构成监控系统。通过DM642独立多媒体接口(MII),片外连接一片以太网处理芯片,就可以构成10/100 Mbpa以太网模块。本地回放由视频编码芯片来完成。

通过DM642的EMIF接口可以连接SDRAM和Flash存储器。尽管DSP提供了片内RAM,但是在大多数情况下不能满足系统的要求;同时对于要求实时处理的系统而言,又要求尽量减小在数据流动过程中由于存储器读写造成的时间开销,因此在系统中配置了高性能的SDRAM,它在运行程序和数据处理时使用。Flash在系统中主要是用来存放系统软件和配置参数的。

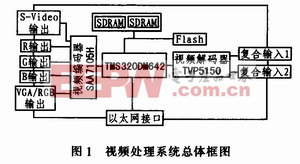

系统的总体框图如图1所示。

在该视频处理系统上集成了相当数量的板上设备以适应不同的应用环境,其主要特点为:

1)系统的运行频率为600 MHzc。

2)2个视频端口:1个为板上解码器,1个为板上编码器。

3)32 MB的同步DRAM空间。

4)2 MB的Flash空间。

5)以太网接口。

6)配有仿真器接口可以用来进行JTAG仿真。

7)供电电压为+5 V。

8)蜂鸣器报警。

1.2 存储器模块设计

在数据处理模块中,DSP芯片、SDRAM芯片和Flash芯片这3块芯片是整个模块电路的核心。该模块的功能是完成与外部数据存储器的数据传输和程序存储器的程序读写任务。通过JTAG接口电路与仿真器相连后接到计算机主机进行仿真调试,实现与目标主机的数据交换。

1.2.1 SDRAM接口设计

在系统的硬件设计中,SDRAM内存芯片选用Micron公司生产的MT48LCAM3282-1Mx32×4 banks。SDRAM,即Synchronous DRAM(同步动态随机存储器),表明它的工作速度是和系统的总线速度同步的。MT48LC4M3282总线最高时钟为166 MHz,它主要用来存储数据和程序,SDRAM的刷新由DSP芯片自动控制。MT48LCAM3282是一款高速CMOS动态随机存储器,它内部配置为4个区的同步接口。

DM642的EMIF可以对SDRAM的地址属性进行编程,它和SDRAM可以实现无缝连接。EMIFA最大的时钟总线可达133 MHz。SDRAM控制器可以支持16 M~256 Mbit的SDRAM芯片。TMS320DM642上的Cache容量有限,所以视频数据通常存放在片外SDRAM中,在需要用到的时候通过EDMA把数据从片外搬移到片内处理,这样就可以提高程序的执行效率四。TMS320DM642的SDRAM接口图如图2所示。

由于TMS320DM642的数据总线是64位,而每片MT48LC4M3282的数据总线是32位,所以需要并联两片MT48LC4M3282才能构成64位的数据总线,这样才可以与TMS320DM642的EMW数据总线相连。参照DM642数据手册中SDRAM的配置方法,EA15、EA16控制SDRAM的组,EA3-EA14控制行地址,EA3-EA11控制列地址,片选信号接到DM642的![]() 上,这样就把SDRAM分配到CE0空间上。

上,这样就把SDRAM分配到CE0空间上。

1.2.2 Flash接口设计

DM642 EMIFA的异步接口为各种存储器和外设类型提供了可配置的存储器周期类型,包括SRAM、EPROM、Flash等,在本系统中Flash采用的是SST公司生产的SST39VF1601 Flash,片选信号接到DM642的![]() 引脚上。当DSP上电后,DSP通过增强的直接存储器访问从外部的CE1寻址空间复制1 K字节的数据传给内部存储空间,然后再从内部存储空间0x0处开始运行,所以Flash ROM必须配置在DSP的CE1空间,在DSP存储器中对应的地址是0x90000000-0x90200000。

引脚上。当DSP上电后,DSP通过增强的直接存储器访问从外部的CE1寻址空间复制1 K字节的数据传给内部存储空间,然后再从内部存储空间0x0处开始运行,所以Flash ROM必须配置在DSP的CE1空间,在DSP存储器中对应的地址是0x90000000-0x90200000。

1.3 JTAG接口设计

JTAG接口是调试环境和目标板之间的接口,它的好处是可以让开发者在对目标板进行开发的同时可以不改变目标板的系统结构,从而方便了系统的开发与测试。XDS510仿真器通过JTAG接口将系统板与电脑连接起来,这样就可以使用TI提供的集成化开发环境对系统进行调试了。JTAG接口采用标准的双排14脚插座。系统的JTAG接口电路如图3所示。

- 基于算法的DSP硬件结构分析(04-02)

- 电力电子装置控制系统的DSP设计方案(04-08)

- LPC2292的μC/OS-II硬件抽象层构建(04-26)

- 基于DSP的宽带雷达多片流水分段脉压处理平台设计(08-02)

- 基于MCU+DSP的运动控制硬件平台设计(10-01)

- 基于DSP和IPM的变频调速系统的硬件设计(11-25)