基于DM642的视频处理系统硬件设计

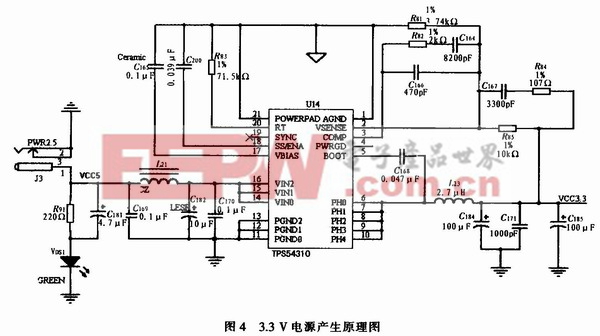

1.4 电源模块设计

DM642需要两种电源,一种是内核电源(1.4 V),另一种是I/O电源(3.3 V)。通常由于DM642用于嵌入式系统中,因此电源电路设计不仅要考虑电压精度、稳定度和外围电路的复杂度等问题,还要考虑低功耗问题。另外,根据设计要求,为了保证芯片正常工作,在系统上电作时,对这两种电源的上电顺序还有一定的要求,如果违反该要求,可能降低器件的性能或永久损坏器件。内核电源要比I/O电源早上电,至少不能晚于I/O电源上电。在电路设计中,通过采用在两个电源之间串联二极管的方法来解决系统上电顺序的问题。

系统设计中,电源芯片采用的是TI公司的TPS54310,它是TI公司生产的一款开关电源调节芯片,它能够实现低电压输入和高电流输出(输人电压范围为3~6 V,输出电压根据需要可以在0.9~3.3 V之间调节,输出电流为3 A)。图4是3.3 V电源产生电路,1.4 V电源产生电路与此类似,只需根据TPS54310中的计算公式将相应的电阻和电容值做相应的修改就可以得到1.4 V电源。3.3V的电源不仅是DM642的0电源,同时也是系统上视频解码芯片、视频编码芯片、SDRAM芯片等的供给电源。

1.5 视频输入输出模块设计

1.5.1 视频输入模块设计

视频输入模块设计采用的视频解码芯片是TVP5150APBS,它是TI公司专门开发的一款可以方便携带的低功耗视频解码芯片,可以广泛用于视频系统的设计。TVP5150APBS的视频输入端可以输入两路复合视频信号或者一路S端子信号。输入信号(如PAL、NTSC等制式)通过增益控制单元、模数转换器和Y/C分离及处理模块后,最后可以转化为8位ITU-R BT.656的数据格式,或者转化为8位4:2:2的数据格式。TVP5150A-PBS的初始化操作是通过操作IIC总线来实现的。TVP5150APBS的IIC地址可以通过控制12CSEL引脚的高低电平来设置。当该引脚是低电平时,IIC地址是0xB8h,当该引脚是高电平时,IIC地址则为0xBAh。TVP5150APBS与TMS320DM642的连接示意如图5所示。

从图5可知,视频信号可从TVP5150APBS的AIP1A或AIPIB输入,数据输出引脚YOUT[0:7]与DM642的VP0[2:9]引脚连接在一起。TVP5150-APBS的系统时钟引脚SCLK与DM642的VPOCLK0引脚连接。因为在本系统的设计中采用的是ITU-R BT.656的视频输出格式,所以在系统中不需要分立的同步信号。因此,TVP5150APBS的HSYNC(行同步信号)、VSYNC(场同步信号)、AVID(行消隐指示信号)以及FIDFig.5 Colleetion bet-ween TVP5150APB5 and DM642(奇偶场指示信号)这几个引脚并不需要与TMS320DM642连接, 只需要将TVP5150APBS的INTERQ引脚与TMS320DM-642的VPOCTL0引脚连接起来。

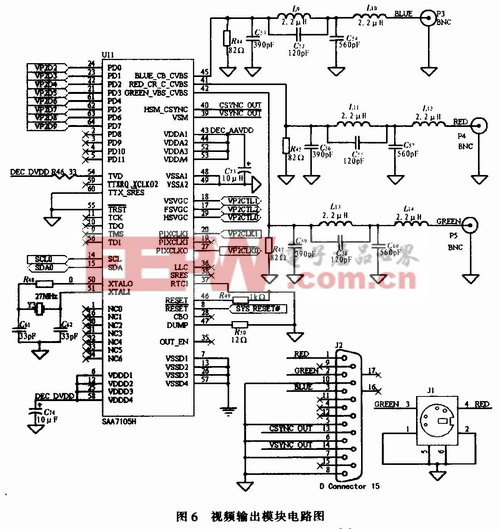

1.5.2 视频输出模块设计

在系统设计中,视频输出模块中的视频编码芯片选用的是Philips公司的SAA7105H,它同时具有SDTV(标准清晰度电视)和HDTV(高清晰度电视)信号编码能力,可以广泛用于视频输出的设计中。视频输出模块的电路如图6所示。

从图6中可知,将DM642的VP2端口配置成视频输出端口。由于VP2端口的数据线与SAA710SH的数据线相互错位,因此这会造成无法正常显示视频输出。为了解决这个问题,在将VP2端口配置成ITU-R BT.656视频输出时,数据就会从VP2 A通道的VPD02-VP2D09输出,VP2D00-VP2D 01则输出无效,因此就需要将VP2D02-VP2D09这8根数据线连接到SAA7105H的PD0-PD7对应的引脚。这样VP2D10-VP2D19在视频回放中就没有使用。

SAA7105H将从DM642端传送来的PC信号转化为PAL制式(50 Hz)或者是NISC制式(60 Hz)送到外部TV端输出。SAA7105H默认为休眠状态,在休眠过程中HC总线仍然可以接受来自DM642的命令。当SAA7105H的3个数模转换器视频输出与外部TV相连接时,SAA7105H能够自动检测到数模转换器接口的阻抗变化,然后通过芯片的TVD(电视信号检测)引脚向TMS320DM642发出中断请求,表明外部有播放要求。此时,DM642就会通过IIC总线来配置SAA7105H的内部寄存器,激活还处于休眠状态的SAA7105H,开始进行本地视频的播放。

在视频输出模块中,SAA7105H的HSVGC(水平同步输出)、VSVGC(垂直同步输出)、FSVGC(帧同步输出)分别于TMS320DM642端口的VP2CTL0、VF2CTL1以及VP2CTL2这3个引脚相连。SAA7105H的输出方式可以有RGB格式、CVBS(混合视频)格式、S-Video格式以及VGA格式等几种。其输出方式的选择通过SAA7105H的应用子地址来控制。

1.6 以太网接口设计

以太网接口设计中的以太网处理芯片采用Intel公司的LXT97lA,它符合IEEE标准,直接支持10 Mbps和100Mbps的双绞线应用,也可以支持100 Mbps的光纤接口。LXT971A与DM642的连接示意图如图7所示,在以太网模块中还需要用到网络变压器和RJ-45以太网连接器。

- 基于算法的DSP硬件结构分析(04-02)

- 电力电子装置控制系统的DSP设计方案(04-08)

- LPC2292的μC/OS-II硬件抽象层构建(04-26)

- 基于DSP的宽带雷达多片流水分段脉压处理平台设计(08-02)

- 基于MCU+DSP的运动控制硬件平台设计(10-01)

- 基于DSP和IPM的变频调速系统的硬件设计(11-25)