单片机典型案例开发(一)

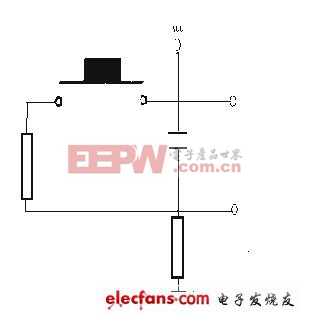

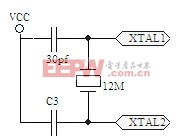

A/D转换的结束信号EOC。ADC0809为逐次比较型A/D转换器,当开始转换时,EOC信号为低电平,经过一定时间,转换结束,转换结束信号EOC输出高电平,转换结果存放与ADC0809内部的输出数据锁存器中。引脚9为A/D转换数据输出允许控制端OE,当OE为高电平时,存放与输出数据存储器中的数据通过ADC0809的数据线D0~D7输出。引脚10为ADC0809的时钟信号输入端CLOCK。在连接时,ADC0809的数据线D0~D7与AT89S51的P0口相连,ADC0809的地址引脚、地址锁存端ALE、启动信号START、数据输出允许控制端OE分别与AT89S51的P2口相连,转换结束信号EOC与AT89S51的P3.7口相连。时钟信号输入端CLOCK信号,由单片机的地址锁存控制端ALE提供。单片机的系统时钟为12MHZ。 IN0-IN7:8条模拟量输入通道 。ADC0809对输入模拟量要求:信号单极性,电压范围是0-5V,若信号太小,必须进行放大;输入的模拟量在转换过程中保持不变,如若模拟量变化太快,则需在输入前增加采样保持电路。 地址输入和控制线:4条 。ALE为地址锁存允许输入线,高电平有效。当ALE线为高电平时,地址锁存与译码器将A,B,C三条地址线的地址信号进行锁存,经译码后被选中的通道的模拟量进转换器进行转换。A,B和C为地址输入线,用于选通IN0-IN7上的一路模拟量输入。 数字量输出及控制线:11条 。ST为转换启动信号,当ST上跳沿时,所有内部寄存器清零;下跳沿时,开始进行A/D转换;在转换期间,ST应保持低电平。EOC为转换结束信号。当EOC为高电平时,表明转换结束;否则,表明正在进行A/D转换。OE为输出允许信号,用于控制三条输出锁存器向单片机输出转换得到的数据。OE=1,输出转换得到的数据;OE=0,输出数据线呈高阻状态。D7-D0为数字量输出线。 CLK为时钟输入信号线。因ADC0809的内部没有时钟电路,所需时钟信号必须由外界提供,通常使用频率为1MHZ,VREF(+),VREF(-)为参考电压输入。 3.5 ADC0809应用说明 ADC0809内部带有输出锁存器,可以与AT89S51单片机直接相连。 初始化时,使ST和OE信号全为低电平。送要转换的哪一通道的地址到A,B,C端口上。在ST端给出一个至少有100ns宽的正脉冲信号。是否转换完毕,我们根据EOC信号来判断。当EOC变为高电平时,这时给OE为高电平,转换的数据就输出给单片机。 3.6 ADC0809工作原理 8路模拟信号由ADC0809的IN0~IN7端输入,AT89S51单片机的ALE端口输出的脉冲信号送ADC0809的10脚作为ADC的时钟信号(产生CLK信号的方法就得用软件来产生)。A/D转换完成之后,从EOC端返回AT89S51一个转换结束信号,单片机随即用信号将A/D转换的数字输出从D0~D7端经P0口数据总线读入自己的存储器中。A/D转换过程全部结束。再经软件程序转换成a~g 7段码输出,驱动LED数码管。各位数码管由位控信号P3.0、P3.1、P3.2、P3.3控制,由74LS245反相驱动将依次巡回点亮数码管。 3.7 复位电路的设计 本设计采用了上电自动复位和手动复位,上电自动复位是再加电瞬间电容通过充电来实现的,其电路如图3.2所示。在充电瞬间,电容C通过复位电阻R充电,RST端出现正脉冲,以复位。只要电源VCC的上升时间不超过1MS,就可以实现自动复位,既接通电源就完成了系统的复位初始化,手动复位是通过按钮实现的。 图3 复位电路 3.8 时钟电路的设计 任何一块单片机的正常工作都离不开时钟信号,本设计中利用8951内部的高增益反相放大器,外加石英晶体以及两个电容就构成了稳定的自激振荡器。给单片机提供了时钟信号,保持单片机按正常的时序工作。 图4 时钟电路

- 嵌入式软件设计中查找缺陷的几个技巧(03-06)

- 基于算法的DSP硬件结构分析(04-02)

- Windows CE下驱动程序开发基础(04-10)

- DSP+FPGA在高速高精运动控制器中的应用(05-17)

- 基于USB接口和DSP的飞机防滑刹车测试系统设计(05-19)

- 一种基于DSP平台的快速H.264编码算法的设计(05-19)