DSP+FPGA在高速高精运动控制器中的应用

运动控制卡已经在数控机床、工业机器人、医用设备、绘图仪、IC电路制造设备、IC封装等领域得到了广泛运用,取得了良好的效果。目前运动控制卡大部分采用8051系列的8位单片机,虽然节省了开发周期但缺乏灵活性,难以胜任高要求运作环境,而且运算能力有限。

DSP的数据运算处理功能强大,即使在很复杂的控制中,采样周期也可以取得很小,控制效果更接近于连续系统。把DSP与PC的各自优势结合将是高性能数控系统的发展趋势。本运动控制器采用TI公司的高性能浮点DSP作为主控芯片,通过ISA接口与PC协调并进行数据交换,以PC计算机作为基本平台,以DSP高速运动控制卡作细插补、伺服控制的核心,对直线电机的运动进行控制,取得了良好的实际应用效果。

1 高速高精运动控制卡的主要硬件构成

本运动控制系统的任务是控制直线电机的运动,要求4轴输入和4轴输出,采用光栅尺对输入计数,16位并行高速DA输出,运动定位精度要求达到10nm,响应时间<100ns。

高速直线电机是本系统的控制对象,它具有加速快(a>10g),运动速度高(v>300mm/s)的特点。要求控制系统有足够短的响应时间(<100ns)和足够高的定位精度(10nm级),因而系统的核心CPU的处理能力及运算能力必须满足高速要求;此外,直线电机运动定位的核心是高精度的反馈控制装置。直线电机的反馈控制装置是光栅尺和高精度脉冲计数器,光栅尺发出与运动距离成线性关系的脉冲数,脉冲计数器的计数值表示直线电机当前的运动位置。经计算,计数长度为28位的计数器才能满足定位的精度要求,同时计数频率很高。一般的通用计数器参数无法达到,所以设计一个特殊计数器是必要的。为了方便设置目标点的运动参数,使运动控制卡具有比较好的人机交互功能,系统必须具有与PC机通信的功能。

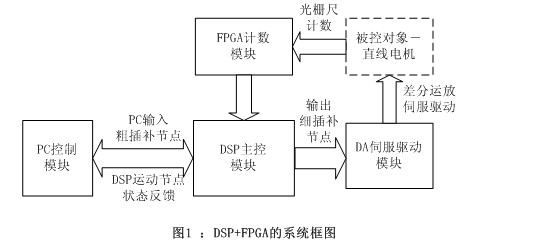

综合考虑上述要求,系统的设计采用DSP+FPGA的形式,由DSP主控芯片作为中央处理模块,FPGA作为反馈计数模块且负责板上的部分逻辑译码工作,PC通信接口模块采用双口RAM,输出模块用D/A转换器实现,如图1所示。

1.1 DSP模块

基于DSP的运动控制系统一般采用TI公司的TMS320C24x系列芯片,但24x系列是16位定点处理器,运算能力有限。不能满足本系统规划的高速高精要求,为此,我们选用了TI公司的TMS320C32 DSP作为主控芯片。

TMS320C3X系列芯片是美国TI公司推出的第一代浮点DSP芯片,具有丰富的指令集、很高的运算速度、较大的寻址空间和较高的性价比,在各领域得到了广泛的应用。TMS320C32是TMS320系列浮点数字信号处理器的新产品,在TMS320C30和TMS320C31的基础上进行了简化和改进。在结构上的改进主要包括可变宽度的存储器接口、更快速的指令周期时间、可设置优先级的双通道DMA处理器、灵活的引导程序装入方式、可重新定位的中断向量表以及可选的边缘/电平触发中断方式等。

对TMS320C32的开发可以用汇编语言,也可以用C语言。使用汇编语言的优点在于运行速度快、可以充分利用芯片的硬件特性,但开发速度较慢,程序的可读性差;而C语言的优势在于编程容易、调试快速、可读性好,可以大大缩短开发周期,但C语言对于其片内的没有映射地址的特殊功能寄存器不能操作,如IF和IE,AR0~AR7等。

1.2 FPGA模块

该部分主要功能为一个4通道的针对光栅尺的脉冲计数器,此外,还承担部分地址译码的工作。但由于脉冲计数频率高,计数量大,所以必须选择高容量、高性能的可编程逻辑器件。

ALTERA FLEX(Flexible Logic Element Matrix)10K 系列FPGA,规模从一万门到十万门,可提供720~5392个触发器及6144~24576位RAM,提供30ns、40ns及50ns等几个速率等级,可适应18~105MHz的信号处理速率。ALTERA FLEX10K系列FPGA主要由输入输出单元IOE、掩埋阵列EAB、逻辑阵列LAB及内部连线组成。EAB是在输入和输出端口加有寄存器的RAM块,其容量可灵活变化。所以,EAB不仅可以用于存储器,还可以事先写入查表值来用它构成如乘法器、纠错逻辑等电路。当用于RAM时,EAB可配制成多种形式的字宽和容量。

LAB主要用于逻辑电路设计,一个LAB包括8个逻辑单元LE,每一个LAB提供4个控制信号及其反相信号,其中两个

可用于时钟信号。每一个LE包括组合逻辑及一个可编程触发器。触发器可被配成D,T,JK,RS等各种形式。IOE提供全局的时钟及清零信号输入端口,还提供具有可编程性的各种输入输出端口,如低噪声端口、高速端口等。

FLEX10K系列芯片是ALTERA公司新近推出的PLD产品。与ALTERA公司先前推出的MAX7000系列EPLD相比,FLEX10K(以下简称10K)系列具有更加丰富的内部资源(最多可达10万门),更加充裕的可配置的I/O管脚(最多达406条)。再加上其低廉的价格,使得10K系列芯片受到越来越多用户的欢迎。

基于以上原因,我们在本方案中采用ALTERA FLEX10K10,并且考虑到以后设计的连续性,我们可以无需更改硬件电路,就可以更换性能更高的、相同尺寸、相同管脚配置的ALTERA FLEX10K20。

1.3 PC通信接口模块

该模块选用16位的ISA总线与PC相连,CY7C133双口RAM用作数据缓冲。

ISA总线的使用十分灵活、方便,而且I/O操作比较简单。虽然ISA总线的引脚多但并不是都要用到的,关键是几个固定引脚的应用,例如:I/O CH RDY、I/OR、I/OW、ALE、数据线和地址线,结合起来实现通信。

在本系统中,双口RAM的 PC端地址线并没有直接采用ISA过来的地址线,而是由FPGA内部地址计数器给定。这是因为,ISA总线上大部分地址都已经被PC系统分配好,直接把2K的双口RAM数据空间映射到ISA总线上并不现实;而且控制系统与PC交换的数据基本上是一系列加工点的坐标参数,采用顺序访问对性能没有影响。因此采用地址计数器方式的顺序访问,完全能够达到设计的要求。

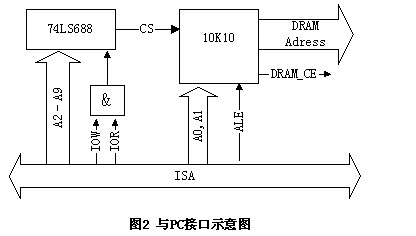

具体做法是:ISA地址线的A2~A9接到地址比较器74LS688,与设定好的地址作比较,74LS688的片选信号由ISA的IOR和IOW的"与"提供(IOR和IOW在ISA总线访问端口时低有效),A0,A1接到FPGA,用于选择FPGA内部4个功能不同的寄存器。ISA的ALE用于触发FPGA 内部逻辑功能,锁存ISA总线过来的信号,如图2所示。

当访问地址清零寄存器时,地址计数值清零;当访问地址增加寄存器时,地址计数值增加"1"。如此类推,访问不同的寄存器就对地址计数值完成不同的操作,把地址计数值直接作为地址送给双口RAM,就可以实现ISA总线访问双口RAM了。

1.4 输出模块

输出模块采用模拟输出,经外部放大驱动电机的方案。D/A转换芯片选择DAC7744。

DAC7744是高性能的4通道16位高速D/A,主要特点如下:

● 输出通道:独立4 路

● 输出信号范围:0~5V;0~10V;±5V;±10V

● 输出阻抗:≤2Ω

● D/A转换器件:DAC7744

● D/A转换分辨率:16位

● D/A转换码制:二进制原码(单极性) 二进制偏移码(双极性)

● D/A转换时间:≤1μs

● D/A转换综合误差:≤0.02% FSR

● 电压输出方式负载能力:5mA/路

1.5 存储模块

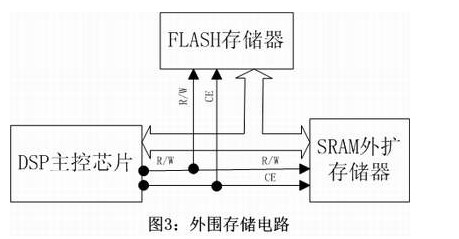

存储模块用于存储系统程序和数据,主要由SRAM(2片CY7C1021)和FLASH(AM29F40

0B)组成。外围存储电路如图3所示。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)