高速红外VFIR控制器的设计与实现

3T)的延时后进行逻辑计算,得到下一状态矢量值N=(s1,s2,s3),即与输入数据有关的N出现在(n+9T)时刻;再经过一个编码周期,即(n+12T)时刻,状态N赋给内部状态矢量S=(s1,s2,s3),同时计算与输入数据码元组d=(d1,d2)有关的内部码字矢量C=(c1,c2,c3),再经过一个编码周期,内部码字C赋给输出码字矢量Y=(y1,y2,y3)。由此可见16Mbps的数据速率经过编码器变为24Mchip/s编码速率,整个编码过程延时5个编码周期即15个chip。注意编码器初始状态S应设置为(1,0,0)。译码器原理:输入数据R=(r1,r2,r3)经过锁存器延时得到矢量Y4=(y10,y11,y12),对Y4进行不同的延时得到Y3、Y2及Y1。这里矢量Yi是Y4的4-I次延时(由锁存器实现延时);对Y4进行或非运算得到Zd,再将Zd进行不同的延时得到Zc和Zb。这里Zc、Zb、Zd是变量,然后将Y4、Y3、Y2、Y1、Zb、Zc、Zd进行逻辑运算、延时分别得到矢量X1=(x1,x2)、X2=(x3,x4)、X3=(x5,x6);最后将x1、x2经过锁存器得到译码器输出矢量值U=(u1,u2)。整个译码过程延时4个周期即12个chip。可见HHH(1,13)编译码电路比较简单,利用FPGA基于门级描述即可实现,但必须注意锁存器时钟fclock=1/3fchip。VFIR模式增加线性反馈移位寄存器(LFSR)实现加扰和解扰功能提高系统性能,减少误码。

3 甚高速红外VFIR控制器的软件设计

控制器软件主要分为三部分:系统初始化部分、接收部分、发送部分。系统初始化首先调用BIOS 1Ah中断功能获取设备PCI总线号、功能号、内存、I/O空间基地址和空间大小以及中断号,然后通过直通(Pass-Thrn)方式写控制命令初始化红外控制器,选择控制器接收或发送数据,设置控制器工作模式和波特率分频数并允许控制器工作。红外控制器具有收发双向数据传输能力。编程时将S5933FIFO设置成由PCI接口初始化为同步主控方式,支持突发传输(DMA);然后根据控制器收/发位判断PCI总线主控读还是主控写操作。程序采用中断控制,主程序调用set_up_pci_busmaster()初始化主控操作,该函数不仅装载访问内存实际地址和传输字节数,而且还要允许读/写传输字节数到零中断。红外控制器初始化完成后,系统等待中断。中断服务处理程序读取S5933中断状态/控制寄存器INTCSR判断中断源,并清除中断标志;读取CRC校验状态位,判断接收数据是否正确。发送数据时,中断服务处理程序还要检测红外发送FIFO状态位是否为1(1表示FIFO为空),不为1置发送不为发空标志tx_not_empty=1,主程序继续等待,直到TXFIFO数据为空;同理接收数据也需要检测红外接口状态寄存器的红色接收FIFO状态位是否为1(测试位为1表示FIFO为空)。这样可保证接收和发送FIFO的数据完全被取走。编写的应用程序使用Turbo C2.0调试通过。

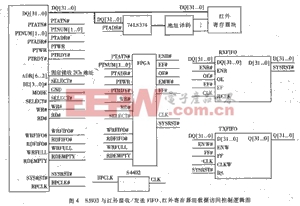

PCI总线已经成为当今电脑的主流总线,为此根据红外串行物理层规范IRDA-1.4设计基本PCI总线的甚高速红外VFIR控制器。使用AMCC公司PCI总线专用控制器外加部分接口控制电路实现VFIR控制器硬件设计,缩短开发周期、提高效率、节约成本。目前正在使用VtoolsD开发虚拟驱动程序,解决系统如何分配红外控制器配置资源、如何访问硬件设备、如何处理硬件中断和总线主控DMA操作以及VXD和应用程序之间的通信。另外国外已有公司推出VFIR红外控制器专用芯片,如MKNET公司的MK7100。

- 一种基FPGA和DSP的高性能PCI数据采集处理卡设计(08-26)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于PCI总线和DSP芯片的图像处理平台的硬件设计(07-06)

- 基于DSP和PCI总线的通用数字信号处理系统(11-13)

- 一种基于PCI总线和DSP技术的虚拟仪器设计(03-16)

- 基于DSP的PCI驱动程序开发 (04-08)