一种基FPGA和DSP的高性能PCI数据采集处理卡设计

时间:08-26

来源:ic72

点击:

1 引言

数据采集处理技术是现代信号处理的基础,广泛应用于雷达、通信、遥测遥感等领域。随着信息科学的飞速发展,人们面临的信号处理任务愈来愈繁重,对数据采集处理系统的要求也愈来愈高。特别是在图像处理、瞬态信号检测、软件无线电等领域,更是要求高速度、高精度、高实时性的数据采集与处理技术。

在传统高速信号处理中,数字信号处理算法一般是通过专门优化的数字信号处理器实现的,目前主要有TI公司的DSP和AD公司的ADSP用于高端信号处理器应用。当这些处理器仍无法满足高速信号处理要求时,可以使用专用的信号处理ASIC芯片,然而使用ASIC在设计上受ASIC厂商设计思路限制,使电路设计变得困难和缺乏灵活性。而最近几年具有乘法器及内存块资源的大容量FPGA以及基于IP核嵌入的FPGA开发技术的出现,可以将嵌入式微处理器、专用数字器件和高速DSP算法以IP核的形式方便的嵌入FPGA,以硬件编程的方法实现高速信号处理算法,这种形式的嵌入为高端应用领域提供了超高性价比的解决方案。

2 高速数据采集处理卡工作原理及主要器件选用

该高速数据采集处理卡是基于DSP+FPGA架构来设计的。FPGA是整个系统的时序控制中心和数据交换桥梁,而且能够实现对底层的信号快速预处理,在很多信号处理系统中,底层的信号预处理算法要处理的数据量很大,对处理速度要求很高,但算法结构相对比较简单,适于用FPGA进行硬件编程实现。而高层处理算法的特点是速据量较低,但算法控制结构复杂,适于用运算速度快、寻址灵活、通信机制强大的DSP芯片来实现。

整个高速数据采集处理系统的主要硬件构成为:高速ADC、RAM、高性能DSP和PCI接口、大容量FPGA。模拟输入经AD采样进入FPGA,经过FPGA里的信号预处理模块处理后进入DSP,由DSP软件进行后续高级算法处理,DSP通过PCI接口与主机交换数据。系统的原理框图如图1所示。

图1:数据采集处理卡总体结构框图

DSP采用TI公司的TMS320C6000系列定点DSP中的TMS320C6416;ADC采用2片AD公司的AD9288,从而实现4路8位采样,最高采样频率为100 MSPS;PCI接口采用TMS320C6416 芯片内集成的PCI2.2控制器,理论最大数据传输速率为132MBps; DSP程序存储在Flash存储器中,器件选用AM29LV160。下面逐一介绍各个主要器件的特性:

2.1 AD9288

AD9288是一款双8bit 高速模数转换器,两个ADC可以独立工作,最高采样率100MSPS,内部集成了跟踪保持电路和基准电路,单电源工作。平行输出接口,兼容TTL/CMOS格式,工业标准温度工作范围, 48PIN LQFP封装。适合应用与高速信号测量仪器,无线通讯设备。

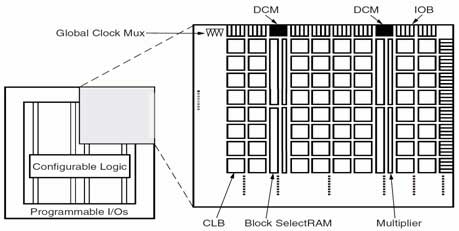

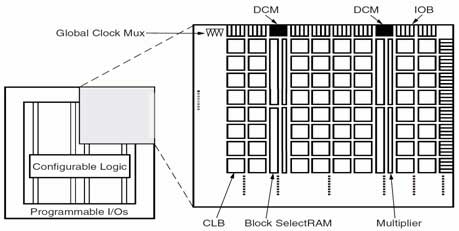

2.2 XC2V1000

单片XILINX公司的XC2V1000芯片,芯片集成度达100万门,具有40个18×18乘法器及40个18Kbit块内存等资源,并有丰富的内部逻辑及路由资源,非常适合实现高速DSP算法,并具有8个DCM可实现复杂的时钟管理,支持不同形式的I/O接口。

图2:Virtex2 结构图

2.3 TMS320C6416

本设计选用的TMS320C6416是TI公司近年推出的高性能定点DSP,其时钟频率达600MHz,最高处理能力4800MIPS,采用先进的甚长指令结构(VLIW)的DSP内核有8个运算功能单元,每个时钟周期可以执行8条指令,所有指令可以条件执行。该DSP具有VITERBI译码协处理器(VCP)和turbo译码协处理器(TCP);采用二级缓存结构,一级缓存(L1)由128Kbit的程序缓存和128Kbit的数据缓存组成,二级缓存(L2)为8Mbit;有2个扩展存储器接口EMIF,一个为64bit(EMIFA),一个为16bit(EMIFB),可以与异步(SRAM、EPROM)/同步存储器的DMA通道;主机接口(HPI)总线宽度可由用户配置(32/16bit),具有32bit/33MHz,3.3V的PCI主从接口,该接口符合PCI标准2.2版,有3个多通道串口(McBSPs),片内还有一个16针的通用输入输出接口(GPIO)。

3 高速数据采集处理系统的硬件连接

3.1 模拟信号输入接口设计

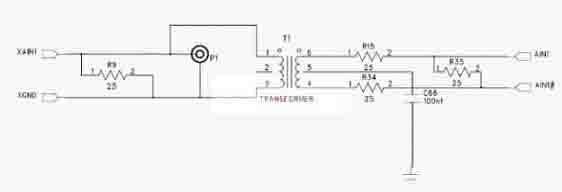

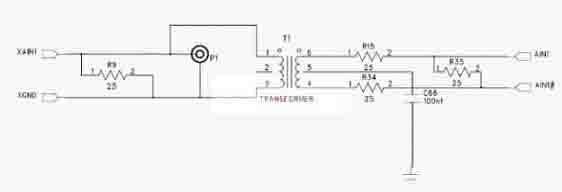

AD9288的模拟信号输入采用差分输入方式。单端输入方式连接比较简单,但抗噪性能差,采取差分输入方式可以尽量减少信号噪声以及电磁的干扰。其AD芯片的单路AD输入电路如图2所示:

图3:模拟信号输入电路

3.2 AD9288与FPGA芯片的连接

AD采样时钟ENC、采样输出数据AD_DATA及输出数据格式选择DFS等控制信号均接入FPGA,由FPGA灵活编程控制AD采样。

图4:AD与FPGA连接结构图

3.3 FPGA 与DSP芯片的连接

DSP 通过EMIFA口数据线、地址线、片选信号及其它接口控制信号与FPGA的IO连接,实现FPGA内部生成FIFO或RAM等缓存组件与DSP连接,该部分电路主要功能是可以将FPGA内存储器映射到DSP地址空间,从而实现DSP对FPGA的直接高速数据交换。另将DSP 外部中断IO信号、及定时器信号接入FPGA,以灵活的实现FPGA与DSP的控制通信。

图5: FPGA与DSP连接结构图

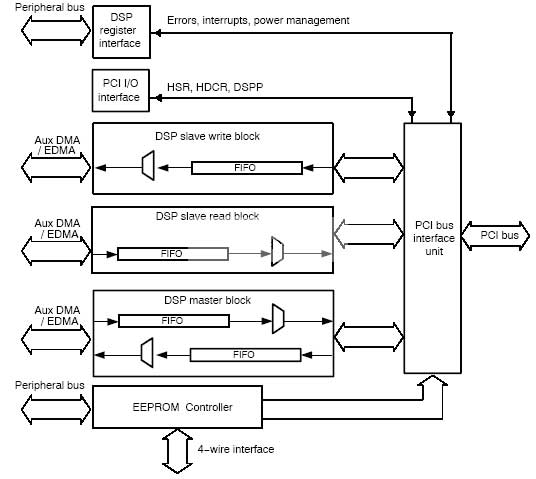

3.4 PCI硬件接口

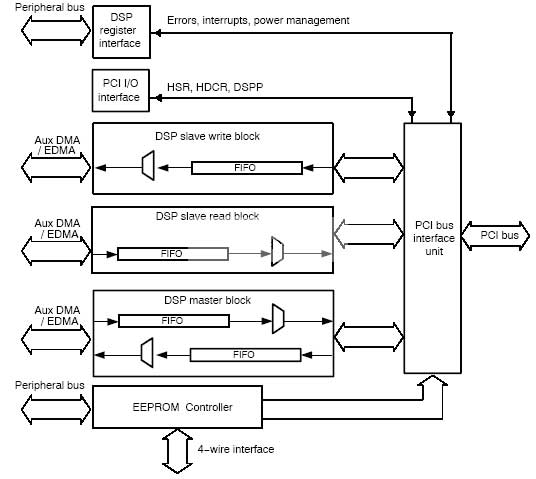

TMS320C6416内部集成33MHz/32位支持PCI主/从接口的PCI2.2接口控制器,无需额外的PCI控制芯片即可方便的与具有PCI接口的主机直接互连。DSP通过内部的EDMA控制器实现集成的PCI接口控制器与DSP的接口。

图6:PCI接口功能模块图

4 PCI接口软件设计

PCI接口开发中有相当大的工作量是关于PCI软件的开发,PCI软件主要包括两方面的工作:驱动程序设计和主机端应用程序的设计。本系统软件的设计目标是实现数据采集卡与主机高速的DMA传输及对主机对DSP内存空间的读写。

4.1 驱动程序设计

驱动程序根据Windows 驱动程序模型(WDM)设计,运行在Win2000 平台上。支持即插即用,采用基于数据包的DMA 传输方式,采用Numega公司的开发包Driver Works和Microsoft公司的2000DDK,并以VC++6.0作为辅助开发环境。

当应用程序请求从采集卡读数据时,内核I/O 管理器将此请求打包成一个IRP(I/O 请求包),驱动程序调用相关例程把应用程序发来控制信息写入DSP设置的控制寄存器,并调用驱动程序的读例程。如果数据处理卡不忙,数据处理卡作为PCI主设备就启动DMA传输;当本次DMA 传输完成时,处理卡产生中断,I/O 管理器调用驱动程序的中断服务例程和DpcForIsr完成此IRP,并从IRP 队列中取出下一个IRP,启动下一次DMA。下一次中断发生时同样处理。这样不断地进行DMA 传输,直到IRP 队列空为止。

4.2 应用程序设计

主机应用程序是主要实现从高速数据采集处理板该取处理后的数据、存储、显示处理及结果以及向数据采集处理板发送控制命令。在Windows 2000下,我们使用的应用程序开发工具是VC++6.0。通过CreatFile()函数得到PCI句柄,用DeviceIoControl()函数来向设备驱动程序发送请求及命令,完成数据的读取与写入。用ReadFile()函数调用驱动启动DMA传输实现高速数据传输。

5 结束语

本高速采集数据处理卡应用了大容量FPGA及高性能数字信号处理器DSP技术和PCI总线技术。DSP是为数字信号处理专门开发的芯片,其内部的总线结构和指令非常适合于数字信号处理,而FPGA高速硬件实现算法的特点使得大容量高速FPGA成为数据处理板级设计重要的选择,PCI接口的高速可靠的传输速率满足了与主机应用软件数据传输的需求。本设计主要是为了软件无线电接收机预研所设计的实验平台,经实际验证,系统运行可靠,是一种比较好的高速数据采集与处理的解决方案,有着广泛的应用前景,也可以用于图像处理、雷达信号处理等数据采集处理领域。

数据采集处理技术是现代信号处理的基础,广泛应用于雷达、通信、遥测遥感等领域。随着信息科学的飞速发展,人们面临的信号处理任务愈来愈繁重,对数据采集处理系统的要求也愈来愈高。特别是在图像处理、瞬态信号检测、软件无线电等领域,更是要求高速度、高精度、高实时性的数据采集与处理技术。

在传统高速信号处理中,数字信号处理算法一般是通过专门优化的数字信号处理器实现的,目前主要有TI公司的DSP和AD公司的ADSP用于高端信号处理器应用。当这些处理器仍无法满足高速信号处理要求时,可以使用专用的信号处理ASIC芯片,然而使用ASIC在设计上受ASIC厂商设计思路限制,使电路设计变得困难和缺乏灵活性。而最近几年具有乘法器及内存块资源的大容量FPGA以及基于IP核嵌入的FPGA开发技术的出现,可以将嵌入式微处理器、专用数字器件和高速DSP算法以IP核的形式方便的嵌入FPGA,以硬件编程的方法实现高速信号处理算法,这种形式的嵌入为高端应用领域提供了超高性价比的解决方案。

2 高速数据采集处理卡工作原理及主要器件选用

该高速数据采集处理卡是基于DSP+FPGA架构来设计的。FPGA是整个系统的时序控制中心和数据交换桥梁,而且能够实现对底层的信号快速预处理,在很多信号处理系统中,底层的信号预处理算法要处理的数据量很大,对处理速度要求很高,但算法结构相对比较简单,适于用FPGA进行硬件编程实现。而高层处理算法的特点是速据量较低,但算法控制结构复杂,适于用运算速度快、寻址灵活、通信机制强大的DSP芯片来实现。

整个高速数据采集处理系统的主要硬件构成为:高速ADC、RAM、高性能DSP和PCI接口、大容量FPGA。模拟输入经AD采样进入FPGA,经过FPGA里的信号预处理模块处理后进入DSP,由DSP软件进行后续高级算法处理,DSP通过PCI接口与主机交换数据。系统的原理框图如图1所示。

图1:数据采集处理卡总体结构框图

DSP采用TI公司的TMS320C6000系列定点DSP中的TMS320C6416;ADC采用2片AD公司的AD9288,从而实现4路8位采样,最高采样频率为100 MSPS;PCI接口采用TMS320C6416 芯片内集成的PCI2.2控制器,理论最大数据传输速率为132MBps; DSP程序存储在Flash存储器中,器件选用AM29LV160。下面逐一介绍各个主要器件的特性:

2.1 AD9288

AD9288是一款双8bit 高速模数转换器,两个ADC可以独立工作,最高采样率100MSPS,内部集成了跟踪保持电路和基准电路,单电源工作。平行输出接口,兼容TTL/CMOS格式,工业标准温度工作范围, 48PIN LQFP封装。适合应用与高速信号测量仪器,无线通讯设备。

2.2 XC2V1000

单片XILINX公司的XC2V1000芯片,芯片集成度达100万门,具有40个18×18乘法器及40个18Kbit块内存等资源,并有丰富的内部逻辑及路由资源,非常适合实现高速DSP算法,并具有8个DCM可实现复杂的时钟管理,支持不同形式的I/O接口。

图2:Virtex2 结构图

2.3 TMS320C6416

本设计选用的TMS320C6416是TI公司近年推出的高性能定点DSP,其时钟频率达600MHz,最高处理能力4800MIPS,采用先进的甚长指令结构(VLIW)的DSP内核有8个运算功能单元,每个时钟周期可以执行8条指令,所有指令可以条件执行。该DSP具有VITERBI译码协处理器(VCP)和turbo译码协处理器(TCP);采用二级缓存结构,一级缓存(L1)由128Kbit的程序缓存和128Kbit的数据缓存组成,二级缓存(L2)为8Mbit;有2个扩展存储器接口EMIF,一个为64bit(EMIFA),一个为16bit(EMIFB),可以与异步(SRAM、EPROM)/同步存储器的DMA通道;主机接口(HPI)总线宽度可由用户配置(32/16bit),具有32bit/33MHz,3.3V的PCI主从接口,该接口符合PCI标准2.2版,有3个多通道串口(McBSPs),片内还有一个16针的通用输入输出接口(GPIO)。

3 高速数据采集处理系统的硬件连接

3.1 模拟信号输入接口设计

AD9288的模拟信号输入采用差分输入方式。单端输入方式连接比较简单,但抗噪性能差,采取差分输入方式可以尽量减少信号噪声以及电磁的干扰。其AD芯片的单路AD输入电路如图2所示:

图3:模拟信号输入电路

3.2 AD9288与FPGA芯片的连接

AD采样时钟ENC、采样输出数据AD_DATA及输出数据格式选择DFS等控制信号均接入FPGA,由FPGA灵活编程控制AD采样。

图4:AD与FPGA连接结构图

3.3 FPGA 与DSP芯片的连接

DSP 通过EMIFA口数据线、地址线、片选信号及其它接口控制信号与FPGA的IO连接,实现FPGA内部生成FIFO或RAM等缓存组件与DSP连接,该部分电路主要功能是可以将FPGA内存储器映射到DSP地址空间,从而实现DSP对FPGA的直接高速数据交换。另将DSP 外部中断IO信号、及定时器信号接入FPGA,以灵活的实现FPGA与DSP的控制通信。

图5: FPGA与DSP连接结构图

3.4 PCI硬件接口

TMS320C6416内部集成33MHz/32位支持PCI主/从接口的PCI2.2接口控制器,无需额外的PCI控制芯片即可方便的与具有PCI接口的主机直接互连。DSP通过内部的EDMA控制器实现集成的PCI接口控制器与DSP的接口。

图6:PCI接口功能模块图

4 PCI接口软件设计

PCI接口开发中有相当大的工作量是关于PCI软件的开发,PCI软件主要包括两方面的工作:驱动程序设计和主机端应用程序的设计。本系统软件的设计目标是实现数据采集卡与主机高速的DMA传输及对主机对DSP内存空间的读写。

4.1 驱动程序设计

驱动程序根据Windows 驱动程序模型(WDM)设计,运行在Win2000 平台上。支持即插即用,采用基于数据包的DMA 传输方式,采用Numega公司的开发包Driver Works和Microsoft公司的2000DDK,并以VC++6.0作为辅助开发环境。

当应用程序请求从采集卡读数据时,内核I/O 管理器将此请求打包成一个IRP(I/O 请求包),驱动程序调用相关例程把应用程序发来控制信息写入DSP设置的控制寄存器,并调用驱动程序的读例程。如果数据处理卡不忙,数据处理卡作为PCI主设备就启动DMA传输;当本次DMA 传输完成时,处理卡产生中断,I/O 管理器调用驱动程序的中断服务例程和DpcForIsr完成此IRP,并从IRP 队列中取出下一个IRP,启动下一次DMA。下一次中断发生时同样处理。这样不断地进行DMA 传输,直到IRP 队列空为止。

4.2 应用程序设计

主机应用程序是主要实现从高速数据采集处理板该取处理后的数据、存储、显示处理及结果以及向数据采集处理板发送控制命令。在Windows 2000下,我们使用的应用程序开发工具是VC++6.0。通过CreatFile()函数得到PCI句柄,用DeviceIoControl()函数来向设备驱动程序发送请求及命令,完成数据的读取与写入。用ReadFile()函数调用驱动启动DMA传输实现高速数据传输。

5 结束语

本高速采集数据处理卡应用了大容量FPGA及高性能数字信号处理器DSP技术和PCI总线技术。DSP是为数字信号处理专门开发的芯片,其内部的总线结构和指令非常适合于数字信号处理,而FPGA高速硬件实现算法的特点使得大容量高速FPGA成为数据处理板级设计重要的选择,PCI接口的高速可靠的传输速率满足了与主机应用软件数据传输的需求。本设计主要是为了软件无线电接收机预研所设计的实验平台,经实际验证,系统运行可靠,是一种比较好的高速数据采集与处理的解决方案,有着广泛的应用前景,也可以用于图像处理、雷达信号处理等数据采集处理领域。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)