最新FPGA的DSP性能介绍

为什么会用FPGA做DSP?Xilinx中国区运营总经理吴晓东从DSP的概念上进行了分析:DSP表示数字信号处理器,也可以表示为数字信号处理-并不代表某一种芯片。实际上,数字信号处理有很多种不同的解决方法,可以用普通的数字信号处理器、MCU(微控制器)等实现,同样,FPGA也可以做数字信号处理。当数字信号处理速度不断提高时,FPGA的应用日益凸显。即FPGA for DSP与DSP互为补充。

Altera亚太区市场渠道工程师王冬刚先生更进一步,甚至乐观地预测,两者不仅互为补充,FPGA可能会对当前的高端DSP形成竞争。他提出:传统DSP正在面临性能、功耗和面市时间的挑战,特别是以下应用:下一代无线通信系统,高端消费类电子,多通道视频系统。用FPGA实现DSP有两大趋势:其一,作为传统DSP协处理,满足系统设备对DSP超高性能的要求;其二,直接取代传统DSP,满足系统对功耗,成本和面市时间的超额要求。

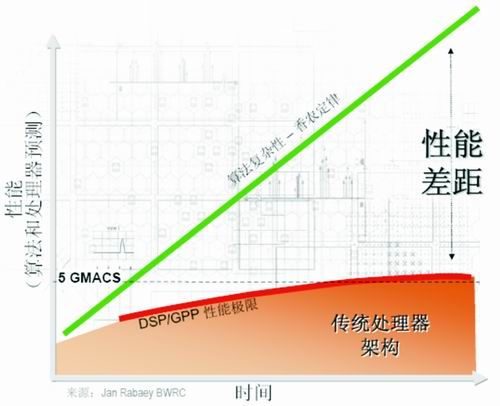

图1 不断发展的DSP处理需求

FPGA做数字处理的特点是什么?对于普通的DSP,数字信号处理主要用一个单元,传统的DSP处理器是一个高性能的数字处理器,里面包括一个高性能的单元可以运行到几个GHz的速度,但是它仅仅是一个单元,当你做比较复杂的运算就可能来回循环几百次才可以做完这个运算(图2下),因此它的速度反而并不很快。

图2 为何FPGA用于DSP

FPGA是一个天生的并行处理结构,FPGA里包含了有几百个单元,例如Xilinx Virtex-5 SXT是550MHz,但可以在一个单元之内迅速把这个复杂的运算一次完成(图2上),所以FPGA的性能实际上是远远高于传统的DSP(图3)。

图3 DSP性能差距

根据令人信服的独立第三方benchmark表明: Altera的器件具有10x/美元的DSP性能。应用FPGA协处理器的系统架

| 构可以卸载传统DSP的工作负载,并且有效执行复杂的数学计算算法,提升DSP系统级效能。 那么,用于DSP(数字信号处理)功能的FGPA与传统的DSP(数字信号处理器)之间是什么关系?FPGA厂商认为:传统的DSP是可编程的DSP,实际上是做信号处理理想的方案;但是随着目前运算的越来越复杂,标准的变化,对于高清、多通道、实时要求越来越高,所以在应用他们方法处理过程中有一个性能空白的地方,而这个地方越来越多的用户在用FPGA实施处理,所以可以认为FPGA和DSP是互为补充的,尤其体现在逻辑的复用和合并方面。 逻辑的复用和合并需要新的外设和不同带宽总线实现的时候,这时用FPGA实现数字信号处理给工程师很大的灵活性,同时FPGA并行处理的能力强大,可帮助DSP做很多性能加速,以解决超负载的问题。这方面,FPGA厂商与TI有一种共识,双方在很多方面是互为补充,共同给客户提供一个更好的解决方案。

图4 高性能DSP FPGA的DSP的演进是这样的:把逻辑固化编程为一个固化的乘法器,然后把它提升更高的阶段,变成一个乘法累加单元(MAC)。为什么这样呢?因为数字信号处理并不是简单的乘法,在做数字信号处理的时候,会碰到很多乘和乘累加,还有比较、计数和矩阵运算等,如果这些都通过乘法器来做的话,需要信号处理的专家和熟悉FPGA的专家才可以做到。 FPGA的DSP的另一个优势是,可以保证能够运行在250MHz以上,上限没有给出,这取决于用户,对一些有经验的用户可以运行到300MHz以上。但是对一个DSP设计人员,由于对FPGA不是很熟悉,也可以轻易运行到250MHz。 Xilinx 8款产品 Xilinx目前有8款FPGA的DSP。其中Sparten-3A DSP为低端产品,今年4月16日刚刚发布。高端的Virtex-DSP分为两个产品线:Virtex-4 SX,采用65nm工艺的Virtex-5 SXT。 很多DSP工程师非常关心DSP的性能够不够高?所以Xilinx的产品从21最多到352个GMAC/s(千兆乘加/秒),以提供不同范围的性能,同时也增大在存储器方面的带宽。因此最低速产品可以运行到250MHz,高速产品运行到550MHz;MAC单元从84到640。 Altera的产品线 高密度Stratix III器件拓展FPGA的DSP性能。嵌入式DSP模块运行在550Hz,这些器件可达到每秒492千兆乘加(GMAC)的性能,并结合良好的逻辑结构与速度优化的互连。 低成本Cyclone III FPGA所提供的好处包括DSP性能、灵活性和更快的面市时间。廉价的Cyclone III ECP3C5拥有足够的嵌入式乘法器和逻辑资源,可以在1080p |

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)