基于DSP和PCI总线的通用数字信号处理系统

时间:11-13

来源:作者:蒋 彦,王 建,刘亚丽

点击:

在信号处理系统中一般采用数据采集卡实现数据采集,采用微机软件处理的方法实现数据处理,采用PC机实现数据管理。由于PC机的CPU采用的是冯?诺依曼存储器结构,并不适用于数字信号的运算,若完全使用PC机处理数字信号不仅造成处理速度慢,影响PC机对数据的管理,还会影响信号处理系统的实时性。因此,提出一种方案把数字信号处理部分从PC机软件中分离出来交给DSP处理,DSP处理完毕后再把数据交还PC机进行管理。这样充分利用DSP对数字信号高速处理的优势,提高信号处理系统的实时性和稳定性。本文以TMS320VC5402 DSP为例,给予说明。

1 系统的硬件设计

1.1 PCI接口芯片PCI9052

PCI9052是一款面向低端应用的高性能、工作在目标(从)模式的PCI接口芯片,支持PCI 2.1总线规范。该芯片的局部总线可以通过编程设置为8/16/32位的(非)复用总线,且局部总线时钟与PCI总线时钟相互独立运行,便于高、低速设备的兼容,并可支持相对慢的局部总线在PCI总线上的突发传输速率达到132 Mb/s。同时,PCI9052提供5个本地地址空间和4个本地地址片选,基址和地址范围可由串行E2PROM编程设置。选择PCI9052作为PCI-DSP桥可以降低PCI总线开发的难度,增加系统的可靠性和稳定性。

1.2 DSP的HPI通信协议

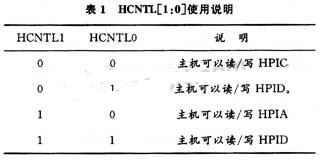

TMS320VC5402 DSP具有8位的增强型HPI接口,其专门用于DSP与其他总线或CPU进行通信。主机是通过HPI控制寄存器(HPIC),地址寄存器(HPIA),数据寄存器(HPID)访问DSP的片内RAM,从而实现与DSP通信的。DSP只能访问HPIC。HPI寄存器的选择由HCNTL[1:0]脚在PCI总线地址有效期实现,说明如表1所示:

1.3 DSP与PCI的接口设计

DSP与PCI的接口是实现DSP与主机进行通信的关键。由于TMS320VC5402 DSP的HPI口是8位并口,所以PCI9052局部总线设定为8位非复用总线模式,并将其LAD[7..0]与DSP的HD[7..0]连接,实现数据总线的连接。接口电路如图1所示。在8位总线模式下,LBE[1:0]分别对应于地址的LA[1:0],将LBE0与HBIL相连,用于区分当前传输的是第1字节还是第2字节。LA[3:2]分别与HCNTL[1:0]相连,用于选择HPI寄存器。利用PCI9052芯片的读写控制信号LBE0#,LBE1#,LW/R,LRDY#和部分地址信号LA[3:2]经过CPLD进行时序和逻辑转换便可生成HPI口的控制信号HBIL,HC-NTL0,HCNTL1,HDS1#,HR/W#。HPIENA脚接"1"表示选用HPI模块。这样PCI9052就可在地址有效期决定访问哪个HPI寄存器,实现DSP与PCI的通信。

1.4 系统的电路设计

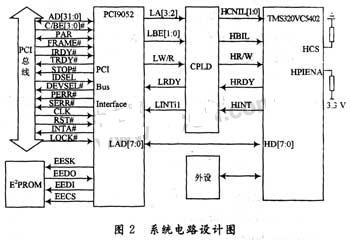

如图2所示系统电路主要由3部分组成:第一部分是PCI9052与PCI插槽间的信号连接电路,包括地址数据复用信号AD[31::0];总线命令信号C/BE[3::0]#;接口控制信号FRAME#,TRDY#,IRDY#,STOP#;IDSEI#,DEVSEL#,错误报告信号PERR#,SERR#;系统信号CLK,RST#。这些信号是局部总线设备保证与PCI总线正确通信的必要信号。第二部分是和串行E-2PROM的信号连接电路,E2PROM内存储的是用于PCI加载的配置信息,这些信息在PCI9052硬件复位时的正确加载是保证PCI局部总线设备正常工作的前提。第三部分是PCI9052与DSP HPI接口的信号连接电路,包括数据线、地址线、读写控制信号线、中断信号线等。此外该系统还可根据DSP的其他功能扩展相应的外设电路。

2 系统的软件设计

2.1 PC机与DSP通信驱动程序设计

PC机上应用软件不能直接对底层硬件进行访问,为实现PC机与DSP的通信还应编写设备驱动程序。WDM(Windows Driver Model)是NT3.51和NT4.0内核模式设备驱动程序模型的扩展形式,是一种PnP驱动程序,能在Windows 98,Windows 2000和Windows XP间实现源代码级兼容。为了便于在多操作系统中均能应用本系统,需编写WDM驱动程序。

在PCI设备驱动程序中主要是完成PCI设备的内存、端口的读写功能和中断处理功能。若采用DDK开发,需要软件人员对计算机底层知识熟悉、开发难度大、为简化驱动程序的开发,可以使用NuMega推出的DriverStudio设备驱动程序开发工具包。通过DriverStudio开发者很容易生成驱动程序框架,同时,DriverStudio与VC++有很好的接口。生成的驱动框架可以在Microsoft VC++6.0环境下添加驱动代完成驱动编写。驱动程序设计内容如下:

PCI设备的硬件资源由PCI配置机构动态分配,由PCI设备实现PCI配置寄存器,提出需要配置的硬件资源,驱动程序只有获取这些资源才能对硬件进行操作。设备初始化环节使PCI设备驱动程序实现识别PCI器件,寻址PCI器件的资源。如果m_MemoryRange0,m_IoPortRange1分别为KMemoryRange类、KIoRange类的实例,则初始化操作可通过调用其成员函数实现:

1 系统的硬件设计

1.1 PCI接口芯片PCI9052

PCI9052是一款面向低端应用的高性能、工作在目标(从)模式的PCI接口芯片,支持PCI 2.1总线规范。该芯片的局部总线可以通过编程设置为8/16/32位的(非)复用总线,且局部总线时钟与PCI总线时钟相互独立运行,便于高、低速设备的兼容,并可支持相对慢的局部总线在PCI总线上的突发传输速率达到132 Mb/s。同时,PCI9052提供5个本地地址空间和4个本地地址片选,基址和地址范围可由串行E2PROM编程设置。选择PCI9052作为PCI-DSP桥可以降低PCI总线开发的难度,增加系统的可靠性和稳定性。

1.2 DSP的HPI通信协议

TMS320VC5402 DSP具有8位的增强型HPI接口,其专门用于DSP与其他总线或CPU进行通信。主机是通过HPI控制寄存器(HPIC),地址寄存器(HPIA),数据寄存器(HPID)访问DSP的片内RAM,从而实现与DSP通信的。DSP只能访问HPIC。HPI寄存器的选择由HCNTL[1:0]脚在PCI总线地址有效期实现,说明如表1所示:

1.3 DSP与PCI的接口设计

DSP与PCI的接口是实现DSP与主机进行通信的关键。由于TMS320VC5402 DSP的HPI口是8位并口,所以PCI9052局部总线设定为8位非复用总线模式,并将其LAD[7..0]与DSP的HD[7..0]连接,实现数据总线的连接。接口电路如图1所示。在8位总线模式下,LBE[1:0]分别对应于地址的LA[1:0],将LBE0与HBIL相连,用于区分当前传输的是第1字节还是第2字节。LA[3:2]分别与HCNTL[1:0]相连,用于选择HPI寄存器。利用PCI9052芯片的读写控制信号LBE0#,LBE1#,LW/R,LRDY#和部分地址信号LA[3:2]经过CPLD进行时序和逻辑转换便可生成HPI口的控制信号HBIL,HC-NTL0,HCNTL1,HDS1#,HR/W#。HPIENA脚接"1"表示选用HPI模块。这样PCI9052就可在地址有效期决定访问哪个HPI寄存器,实现DSP与PCI的通信。

1.4 系统的电路设计

如图2所示系统电路主要由3部分组成:第一部分是PCI9052与PCI插槽间的信号连接电路,包括地址数据复用信号AD[31::0];总线命令信号C/BE[3::0]#;接口控制信号FRAME#,TRDY#,IRDY#,STOP#;IDSEI#,DEVSEL#,错误报告信号PERR#,SERR#;系统信号CLK,RST#。这些信号是局部总线设备保证与PCI总线正确通信的必要信号。第二部分是和串行E-2PROM的信号连接电路,E2PROM内存储的是用于PCI加载的配置信息,这些信息在PCI9052硬件复位时的正确加载是保证PCI局部总线设备正常工作的前提。第三部分是PCI9052与DSP HPI接口的信号连接电路,包括数据线、地址线、读写控制信号线、中断信号线等。此外该系统还可根据DSP的其他功能扩展相应的外设电路。

2 系统的软件设计

2.1 PC机与DSP通信驱动程序设计

PC机上应用软件不能直接对底层硬件进行访问,为实现PC机与DSP的通信还应编写设备驱动程序。WDM(Windows Driver Model)是NT3.51和NT4.0内核模式设备驱动程序模型的扩展形式,是一种PnP驱动程序,能在Windows 98,Windows 2000和Windows XP间实现源代码级兼容。为了便于在多操作系统中均能应用本系统,需编写WDM驱动程序。

在PCI设备驱动程序中主要是完成PCI设备的内存、端口的读写功能和中断处理功能。若采用DDK开发,需要软件人员对计算机底层知识熟悉、开发难度大、为简化驱动程序的开发,可以使用NuMega推出的DriverStudio设备驱动程序开发工具包。通过DriverStudio开发者很容易生成驱动程序框架,同时,DriverStudio与VC++有很好的接口。生成的驱动框架可以在Microsoft VC++6.0环境下添加驱动代完成驱动编写。驱动程序设计内容如下:

PCI设备的硬件资源由PCI配置机构动态分配,由PCI设备实现PCI配置寄存器,提出需要配置的硬件资源,驱动程序只有获取这些资源才能对硬件进行操作。设备初始化环节使PCI设备驱动程序实现识别PCI器件,寻址PCI器件的资源。如果m_MemoryRange0,m_IoPortRange1分别为KMemoryRange类、KIoRange类的实例,则初始化操作可通过调用其成员函数实现:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)