基于TMS320C6000系列DSP的维特比译码程序优化设计

时间:09-27

来源:电子技术应用 作者:张 丹 曹志刚

点击:

卷积码因为其编码器简单、编码增益高以及具有很强的纠正随机错误的能力,在通信系统中得到了广泛的应用。基于最大似然准则的维特比算法(VA)是在加性高斯白噪声(AWGN)信道下性能最佳的卷积码译码算法,也是常用的一种算法[1~2]。

一般来说,实现软判决维特比译码可以有三种方案供选择:专用集成电路(ASIC)芯片、可编程逻辑阵列(FPGA)芯片以及数字信号处理器(DSP)芯片。参考文献[3]对这三种方案的优劣做了详细的比较。使用DSP芯片实现译码是最为灵活的一种方案,但速度也是最慢的,因为整个译码过程都是由软件来实现的。

在近年来兴起的软件无线电技术中,要求采用可编程能力强的的器件(DSP、CPU等)代替专用的数字电路。对信道编解码而言,这样做的优点在于只需要在程序上加以少量改动,就可以适应不同的编码速率以及各种通信系统所要求的不同的编解码方法。然而速度的瓶颈限制了DSP译码在实时系统中的应用,因此提高DSP的译码速度对于软件无线电有着重要的意义。本文的目的就是通过对译码程序结构优化,来提高DSP芯片执行VA算法的速度。

1 维特比译码器

首先,需要定义两个将在本文中用到的术语[2]:

输入帧--每次输入译码器的比特;

输出帧--对应一个输入帧,译码器输出的比特。

图1所示是卷积码译码器(VA算法)的一种典型结构。

1.1 支路度量计算单元(BMG)

计算当前输入帧对应的128条支路的路径度量值,并将其存入支路度量存储单元(BMM)。

1.2 加比选单元(ACS)

将支路度量值与相连的前面的路径度量值相加得到延伸后的新路径的度量值;比较连接在同一个状态上的两条新路径的度量值;选择其中度量值较小的那条路径(幸存路径),并将它的度量值存储到新路径度量存储器(SM)中,幸存路径值(对应编码状态的输入比特)存储到路径存储器(PM)中。

1.3 幸存路径计算单元

找到64条幸存路径中度量值最小的一个(最大似然路径),通过回溯操作(Traceback)在PM中找出该路径对应的所有输入比特,依次输出即为译码结果。

每输出一帧,都对应着一次支路单元计算和64次ACS操作。ACS操作在总的运算时间里占了很大的比例。程序优化的主要工作就是设法减少每个ACS操作所需要的时钟周期数。

2 TMS320C6000 DSP芯片的特点

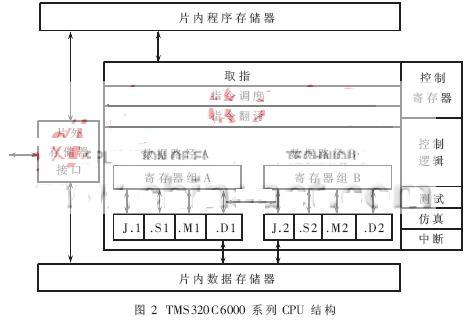

TMS320C6000系列DSP是基于TMS320C6000平台的32位浮点DSP处理器[4]。它包含两个子系列:用于定点计算的TMS320C62x系列和用于浮点计算的TMS320C67x系列。TMS320C6000系列CPU结构如图2所示。时钟频率最高可达到250MHz。该系列DSP包含两个通用的寄存器组A和B,每组有16个32位的寄存器。芯片内含8个运算功能单元:两个乘法器(.M1和.M2);六个算术逻辑单元(.L1 .L2 .S1 .S2 .D1 .D2)。所有单元都能独立并行操作。以TM320C6701为例,它的工作频率最高为167MHz,最快速度可达8×167=1336MIPS。

(1)功能模块的限制 8个功能模块能够执行的指令不尽相同。在实际程序中,由于程序流程的限制,指令的位置不能随便调换,因此不可能在每一个时钟周期都让8个模块同时工作。程序优化的主要手段就是要提高指令的并行程度,即平均每一周期内同时执行的指令数。

(2)交叉路径(Cross Path)的限制 每一个功能模块都只能对其所属的寄存器组中的寄存器进行直接操作。例如.L1只能将结果直接写入寄存器组A。如果要对另一个寄存器组执行读或写操作,需要用到"交叉路径",而整个CPU中只有两条交叉路径。也就是说,一个周期内至多能同时容纳两个相反方向的交叉读写。

(3)多周期指令的限制 LD命令的功能是将数据从存储器读到寄存器中,由.D模块执行。但执行LD命令后必须等待4个周期才能得到需要的数据。类似这样的需要多个周期才能完成的命令(例如跳转指令B)都成为提高指令并行处理程度的障碍。

(4)对长数据操作的限制 C6000指令集只能以8比特、16比特、32比特或者40比特为单位对数据进行操作。

3 VA在DSP上的优化实现

ACS操作是整个VA算法中运算量最大的部分。在通常的程序设计中,使用一种对称的蝶形运算实现ACS操作,每次可以完成两个ACS操作[5]。因此优化的核心任务就是减少每个蝶形运算所消耗的运算周期数。

蝶形运算的原理请参见图3。对前一级的两个相邻状态2i和2i+1,一共有四条支路。计算出四条支路与接收信号的欧氏距离,与两个前一级状态2i和2i+1中存储的以前路径的度量值相加得到四条路径A1、A2、B1、B2的度量值。然后在对应的两个当前状态i和i+32下两两比较,每个当前状态都留下度量值较小的一条路径(幸存路径),同时将当前状态的度量值以及与幸存路径对应的输入比特存入相应的位置,准备下一级计算。

一般来说,实现软判决维特比译码可以有三种方案供选择:专用集成电路(ASIC)芯片、可编程逻辑阵列(FPGA)芯片以及数字信号处理器(DSP)芯片。参考文献[3]对这三种方案的优劣做了详细的比较。使用DSP芯片实现译码是最为灵活的一种方案,但速度也是最慢的,因为整个译码过程都是由软件来实现的。

在近年来兴起的软件无线电技术中,要求采用可编程能力强的的器件(DSP、CPU等)代替专用的数字电路。对信道编解码而言,这样做的优点在于只需要在程序上加以少量改动,就可以适应不同的编码速率以及各种通信系统所要求的不同的编解码方法。然而速度的瓶颈限制了DSP译码在实时系统中的应用,因此提高DSP的译码速度对于软件无线电有着重要的意义。本文的目的就是通过对译码程序结构优化,来提高DSP芯片执行VA算法的速度。

1 维特比译码器

首先,需要定义两个将在本文中用到的术语[2]:

输入帧--每次输入译码器的比特;

输出帧--对应一个输入帧,译码器输出的比特。

图1所示是卷积码译码器(VA算法)的一种典型结构。

1.1 支路度量计算单元(BMG)

计算当前输入帧对应的128条支路的路径度量值,并将其存入支路度量存储单元(BMM)。

1.2 加比选单元(ACS)

将支路度量值与相连的前面的路径度量值相加得到延伸后的新路径的度量值;比较连接在同一个状态上的两条新路径的度量值;选择其中度量值较小的那条路径(幸存路径),并将它的度量值存储到新路径度量存储器(SM)中,幸存路径值(对应编码状态的输入比特)存储到路径存储器(PM)中。

1.3 幸存路径计算单元

找到64条幸存路径中度量值最小的一个(最大似然路径),通过回溯操作(Traceback)在PM中找出该路径对应的所有输入比特,依次输出即为译码结果。

每输出一帧,都对应着一次支路单元计算和64次ACS操作。ACS操作在总的运算时间里占了很大的比例。程序优化的主要工作就是设法减少每个ACS操作所需要的时钟周期数。

2 TMS320C6000 DSP芯片的特点

TMS320C6000系列DSP是基于TMS320C6000平台的32位浮点DSP处理器[4]。它包含两个子系列:用于定点计算的TMS320C62x系列和用于浮点计算的TMS320C67x系列。TMS320C6000系列CPU结构如图2所示。时钟频率最高可达到250MHz。该系列DSP包含两个通用的寄存器组A和B,每组有16个32位的寄存器。芯片内含8个运算功能单元:两个乘法器(.M1和.M2);六个算术逻辑单元(.L1 .L2 .S1 .S2 .D1 .D2)。所有单元都能独立并行操作。以TM320C6701为例,它的工作频率最高为167MHz,最快速度可达8×167=1336MIPS。

(1)功能模块的限制 8个功能模块能够执行的指令不尽相同。在实际程序中,由于程序流程的限制,指令的位置不能随便调换,因此不可能在每一个时钟周期都让8个模块同时工作。程序优化的主要手段就是要提高指令的并行程度,即平均每一周期内同时执行的指令数。

(2)交叉路径(Cross Path)的限制 每一个功能模块都只能对其所属的寄存器组中的寄存器进行直接操作。例如.L1只能将结果直接写入寄存器组A。如果要对另一个寄存器组执行读或写操作,需要用到"交叉路径",而整个CPU中只有两条交叉路径。也就是说,一个周期内至多能同时容纳两个相反方向的交叉读写。

(3)多周期指令的限制 LD命令的功能是将数据从存储器读到寄存器中,由.D模块执行。但执行LD命令后必须等待4个周期才能得到需要的数据。类似这样的需要多个周期才能完成的命令(例如跳转指令B)都成为提高指令并行处理程度的障碍。

(4)对长数据操作的限制 C6000指令集只能以8比特、16比特、32比特或者40比特为单位对数据进行操作。

3 VA在DSP上的优化实现

ACS操作是整个VA算法中运算量最大的部分。在通常的程序设计中,使用一种对称的蝶形运算实现ACS操作,每次可以完成两个ACS操作[5]。因此优化的核心任务就是减少每个蝶形运算所消耗的运算周期数。

蝶形运算的原理请参见图3。对前一级的两个相邻状态2i和2i+1,一共有四条支路。计算出四条支路与接收信号的欧氏距离,与两个前一级状态2i和2i+1中存储的以前路径的度量值相加得到四条路径A1、A2、B1、B2的度量值。然后在对应的两个当前状态i和i+32下两两比较,每个当前状态都留下度量值较小的一条路径(幸存路径),同时将当前状态的度量值以及与幸存路径对应的输入比特存入相应的位置,准备下一级计算。

TMS320C6000系列 DSP 维特比译码 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)