基于Nios II的Boost型功率因数校正系统研究

摘要:分析了基于双环Boost型功率因数校正(PFC)的控制原理及小信号模型,建立了基于PI调节的Boost型PFC控制系统。由于现场可编程门阵列(FPGA)可将Nios II软核处理器及PWM等外设集成到系统主控芯片,从而使系统具有控制精度高、可靠性好等优点。在此基础上,设计了基于Nios II的Boost-PFC硬件电路,并搭建了相应的实验平台进行系统实验。实验结果表明,该系统校正后的功率因数高,达到了理论设计要求。

关键词:功率因数校正;数字控制;现场可编程门阵列

1 引言

PFC技术是减小谐波污染问题的有效方法之一。将PFC技术与数字控制技术相结合,实现数字化的PFC控制系统,已成为电力电子技术的一个重要研究方向。随着微电子和半导体生产工艺的提高,多数集成电路设计已进入片上可重构系统时代,从而使计算机进入微控制领域成为现实。在此基础上,新型电力电子功率器件不断出现,使得采用全控制的开关功率元件进行PWM控制方式成为主流。传统PWM控制大多采用单片机及高性能的DSP来实现,但由于单片机内部系统体系结构和计算功能等条件有限,使其在实现高效控制算法等方面遇到了困难。而DSP需要使用大量的外围电路,并且系统的可升级性较差。

EDA技术不断发展,使得基于FPGA的数字系统为PFC系统的控制提供了一种新的有效方法。该方法就是在PFC系统中,将Nios II及PWM等外设集成到系统主控芯片EP2C8Q208C8型FPGA内,使得系统体积更小,成本低,可靠性高,更适合嵌入式系统的要求,而且具有现场可编程性,能够进行升级换代,具有广阔的应用前景。

2 Boost型功率因数校正系统原理及建模

2.1 系统总体控制方案

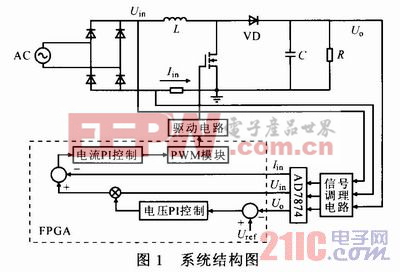

Boost PFC电路是现在应用最广泛的有源PFC电路,具有功率因数值高,总谐波失真小,效率高的优点。该系统采用平均电流控制方式,工作在电感电流连续状态,开关管电流有效值小、EMI滤波器体积小,应用FPGA数字芯片,其相对较复杂的控制也能较好地实现。为实现控制策略,系统需检测整流输入电压Uin,输入电感电流Iin和直流输出电压Uo。瞬时信号Uin,Iin,Uo分别从主电路上得到检测,并经信号调理电路送至AD7874的3条A/D转换通道。经过数字化采样后的Uo信号与输出参考电压信号Uref进行比较,信号差送入电压外环的PI调节器。该环节传递函数的输出与Uin采样值相乘,生成电流内环所必需的参考电流值Iref。Iin经数字采样后,与Iref进行比较,运算结果送入电流内环PI调节器。该PI调节器输出送入PWM比较器,与三角波信号比较产生开关信号的占空比,最后通过驱动电路产生驱动信号控制开关管的通断,实现电路的PFC,系统结构如图1所示。

2.2 Boost PFC模型建立

为实现Boost PFC的双环PI数字控制,系统采用简化的小信号模型建模。要得到Boost变换器的小信号模型,首先要得到平均法模型,然后进行小信号扰动分析。先分别对开关S导通时的电感电压和开关S关断时的电容电流进行积分,再除以周期Ts,即可得到它们在一个Ts内的平均模型,加入扰动并忽略高阶项,可得该电路的动态小信号模型为:

式(2)中第1式中d(s)Uo,(1-D)uo(s),量很小;式(2)中第2式中d(s)I,(1-D)i(s)量很小,将其忽略,即可得到电感电流和输出电压对脉宽变化的传递函数:![]()

此处电压环和电流环调节均采用经典PI调节器,其结构简单,容易实现,将式(3)两式进行Z变换可分别得到电流和电压环的离散数学模

型,由此可根据系统要求分别求出电流环PI参数和电压环PI参数。用VHDL语言在FPGA中编写PI控制器程序,由于其软件设计的灵活性,PI调

节参数能不断得到修正和改进。

3 基于NiosⅡ的Boost-PFC硬件电路

主电路采用Boost拓扑结构,其特点为输入电流连续,传导噪声低及良好的输入波形。在主电路中,电流和电压检测采用霍尔元件实现,经处理后送入A/D采样单元。驱动电路采用TLP250实现主电路与FPGA之间的隔离,保证了功率器件的可靠关断。

3.1 NiosⅡ嵌入式硬件系统构建

EP2C8Q208C8型FPGA资源配置丰富,在该芯片上可嵌入Nios II软核处理器。实验证明嵌入的Nios II软核主频可平稳运行在120 MHz,可满足PFC系统要求。

实验采用QuartusII 9.0作为硬件开发平台,利用SOPC Builder工具构建Nios II嵌入式硬件系统,SOPC Builder允许用户选择和自定义系统模块的各个组件和接口。用户可以很方便地将处理器、存储器和其他外设模块连接起来,形成一个完整的系统。在此先后将CPU,SDRAM模块和EPCS控制器等IP核添加到系统中,从而构建了一个标准的Nios II最小系统。

最小系统建立后,根据PFC系统要求,还需定制PWM外设。在PFC系统中,系统经A/D前端处理及A/D转换后送入Nios II中进行运算,其输出再经过PWM比较器加到驱动电路上,以控制开关管导通和关断,从而使输入电流的波形与输入电压波形基本一致,使电流谐波减少,提高了输入端的功率因数。在自定制PWM外设时,先用VHDL语言编写PWM外设文件,编写完毕后对代码进行编译和仿真。

验证正确后,将其加入SOPC Builder中,做为Avalon外设,之后SOPC Builder生成整个Nios II嵌入式硬件系统。用Quartus II软件编译SOPC硬件系统,生成FPGA的配置文件,将其下载到开发板中的串行电可擦除Flash存储芯片中,便完成了系统硬件平台设计。

3.2 A/D采样控制电路

在PFC系统中需采样输入电压、输入电流和输出电压3路实时信号,故需要3通道A/D转换器,而AD7874是4通道12位同步数据采集器,其特性可满足该系统要求,故选择AD7874作为采样控制器。在A/D采样控制中,用Nlos II作为主处理器,主要完成数据和信息的收集和转发功

能,用FPGA对采集的信号做预处理,并将数据存储在高速FIFO中,从而实现数据的高速采集和目标提取,A/D采样电路框图如图2所示。

校正 系统 研究 因数 功率 Nios II Boost 基于 相关文章:

- 开关电源功率因数校正的DSP实现(01-22)

- 基于CORDIC算法的光相位检测及FPGA实现(06-05)

- s3c2440的触摸屏校正与测试(11-20)

- 时间交替ADC系统的实现(09-12)

- 径向量仪校正工件坐标原点的方法(01-08)

- 使用数字荧光示波器调试功率因数校正电路(02-13)