FPGA在电梯控制系统中的应用

std_logic;

light:in integer range 3 to 1;

segout:out std_logic_vector(6 downto 0));

end component;

begin

u1:fenpin port map(clk,templ0,templ2);

u4:fangdou port map(templ0,uo,temp1);

u5:fangdou port map(templ0,ut,temp2);

u6:fangdou port map(templ0,dt,temp3);

u7:fangdou port map(templ0,dth,temp4);

u8:fangdou port map(templ0,o,temp5);

u9:fangdou port map(templ0,t,temp6);

u10:fangdou port map(templ0,th,temp7);

u11:bigmain port map(temp1,temp2,temp3,

temp4,temp5,temp6,temp7,pres,clk,templ2,

templ1,lu,ld,arr);

u12:display port map(clk,templ1,lightout);

end;

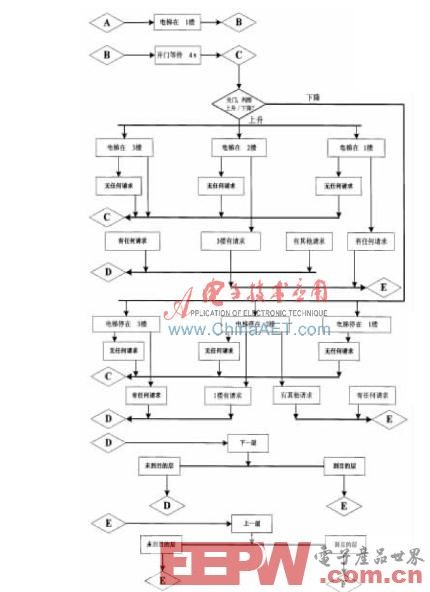

2.3主模块设计

控制模块是整个设计的核心部分,本设计采用状态机[2]的方法来实现。依据电梯的功能要求,这里将电梯的工作分为10个状态。状态机如图2所示。(1)控制模块有两个进程:k1控制输入,无论电梯在什么状态均能接收用户的输入请求,该进程由1 MHz的时钟触发;k2控制电梯的升、降、停留,该程序由1 Hz的时钟触发。(2)进程k1是由1MHz的时钟作为触发沿,不断地检测用户是否有输入请求,对于一、二、三层信号,分别有flag1、flag2、flag3和clear1、clear2、clear3两套标志位来控制输入请求是否有效,是否应该对标志位清零。程序有两个表示电梯的状态:一是位置状态,二是运行状态。

- ALTERA FPGA在微处理器系统中的在应用配置(07-09)

- 藏在系统核心芯片中的DRAM控制器(12-10)

- 真实环境中的系统设计(09-09)

- IoT促进了低功耗的发展(12-05)

- 闪存革命无处不在(12-25)

- 悬崖边上的CPU设计师: 现在该往哪里去?(11-10)