IoT促进了低功耗的发展

时间:12-05

来源:互联网

点击:

Ron Wilson,总编辑,Altera 公司

现在很难在某一次会议上听不到或者看不到关于物联网(IoT)和可穿戴式计算的讨论。但是,请读下去。当人们还在争论IoT设备5年内是会达到200亿规模还是40亿规模的时候,一个意外的挑战已经浮出水面。人们都认为市场上最新的半导体技术也是您下一设计最好的工艺技术。这种想法促进了IoT的雪崩式发展。

最近在硅谷举行的TSMC辅助支持系统论坛上清楚的阐述了这种发展。随着20、16和10 nm工艺的发展,最大的代工线负责人宣称,在老工艺尺寸基础上,不到5个低功耗新工艺代就回到了180 nm。为什么——为什么这么多?在小系统设计中,这些问题构成了新现实。

对电源的其他分析

并不是IoT发起了低功耗工作模式。多年以来,超低功耗微控制器领域就有此类产品。但是,大肆的宣传使得业界特别关注低功耗问题的两个方面:在很多IoT和可穿戴节点上以极低功耗可靠的工作,还有非常低的占空比。

极低功耗需求的来源不同寻常:能量收集。一些IoT设计人员并没有费劲的将电池装到极小的封装中或者难以企及的空间里,而是选择从节点环境中收集能量。他们使用了小型光电池,从周围光中收集能量,采用热电变换器转换浪费的热量,使用惯性发电机把运动转换为电流,还有一些其他手段。一般的结果是可靠的少量电源——至少结合了小的可充电电池和超级电容。

如果您能够将节点耗电保持在一定的功率预算范围内,从很实用的热电转换器的几百µW到光线暗淡的室内微小光电池的几个µW,那么这种策略避免了换电池等问题。

作为对比,较低的占空比并不是约束而是机遇。一般而言,距离数据中心越远,节点的大部分空闲的时间就越长。数据中心的目标应该是不低于80%的利用率。但是在今年的热点芯片大会上,ARM® CTO Mike Muller估计CPU浏览网页的平均工作时间是7%,MP3回放任务大约是3%。距离核心越远,IoT节点对空气温度进行周期性采样时,可能每小时只有几个毫秒在工作,占总时间的百万分之一。

很明显,低占空比应该是降低能耗的好机会。问题是怎么办。要解决这一问题,我们得回到工艺技术和超低功耗问题上。

研究占空比

在低占空比系统中,降低能耗(从而延长电池使用寿命)最高效的策略与您的老奶奶处理电费的策略一样:不使用时关掉它。但是这种好建议的背后却涉及到详细的规划和某些困难的决定。

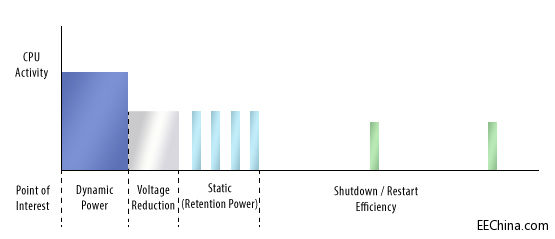

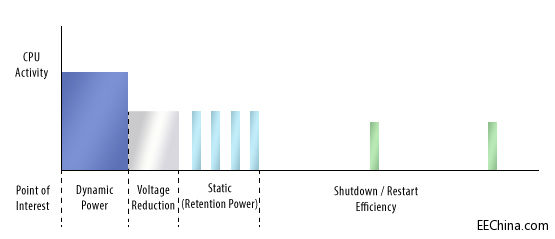

关掉电源意味着将状态存储到非易失存储器中,除非您设计的节点不需要持续的状态信息就能够工作。但是保存状态需要花费时间和能耗,写入闪存会需要很大的突发能耗,这也要有大功率能源。因此,这并不总是可行的——特别是空闲时间很短或者不可预测的情形。在这些情形中,您可能需要保持数据的低功耗模式,包括在状态机中和在存储器中(图1)。这也是老节点及其大规模晶体管再次被关注的原因。

图1.不同的占空比强调了功耗的不同方面。

这些大规模晶体管内在的一个特性是低泄漏电流。如果您的服务器一直以fMAX运行,那么低泄漏并不是很重要,这是因为高速和低动态功耗并不是老工艺关注的重点。但是,如果您设计低占空比系统,大部分时间处于数据保持模式,您不得不延长小电池的使用时间,与动态功耗或者最初的性能相比,您更关心静态泄漏。

这一事实解释了为什么有太多的工艺选择。在180 nm,泄漏几乎没有,但是动态功耗相对较高,而fMAX较低。在28 nm,泄漏比较起来非常高——即使是TSMC针对28 ULP设计的改进型低泄漏晶体管,但是动态功耗和速度要好很多。您可以看一下您规划的占空比,选择您的工艺技术。

当然,并不会非常简单。在体系结构和实施的每一阶段,都会有一些因素影响占空比。例如,您可以禁止中断状态机或者ARM Cortex®-M0等极低功耗MCU,只中断主CPU,以处理触发了重要代码的关键事件。您可以选择无线网络,支持节点在大部分时间进入休眠状态,而不让它一直处于准备响应某一消息的状态。您可以使用硬件加速器来缩短占空比的工作部分。还可以把上游任务放到无线集线器或者云端。

相反,您也可以重新调整占空比。例如,可以放慢时钟以节省功耗,让任务非常慢的运行,从而不会进入休眠模式。或者,可以选择轮询节点,就像带着安眠药的夜班护士,让节点一直保持工作。

总之,要找到动态功耗、运行和空闲以及关断时间、工艺技术的最佳组合会是一件很难的事情。对于ARM的big.LITTLE多核CPU配置等方法,支持您在功能强大的内核中迅速运行较难的线程,然后对于后台任务,切换到较慢的低功耗内核。在某些点,您会有很多选择。

不论占空比还是处理器怎样安排,有一种策略具有明显的优势。对于静态和动态功耗,电压是公式中的二次项。如果您降低Vdd,fMAX就会下降,功耗也是如此。这一点解释了TSMC超低功耗产品的重要特性:其特性是能够工作在非常低的电压下,实际上,接近阈值。

近阈值挑战

据TSMC研发副总裁Cliff Hou,在0.7-0.5V范围内Vdd的准备过程需要很多工作。公司关注的是从高阈值晶体管中获得最佳性能。但是也要处理其他两个主要问题;时序变化和SRAM拓扑。

接近阈值工作的MOSFET驱动负载的时间要长一些。这一简单的物理现象将大部分处理器的时钟频率限制在1 MHz附近。但是,Hou指出还有另一个问题。他解释说,“接近阈值时,波形是非线性的。对此,需要调整静态时序分析,这样,芯片设计人员不用改变他们的方法。”

Hou说,对时序进行了很大的改动后,自然需要检查所有IP在接近阈值电平时能否正常工作。他报告说,“一般而言,检查进行的比较顺利。但是,我们注意到,某些单元——那些有三至四级的,使用了传输逻辑门的,在接近0.5V时会出现问题。”

SRAM有不同的问题:不同的电压电平需要不同的单元设计。一般具有读写辅助功能的SRAM单元在较高电压时能够很好的工作。但是接近0.5V时,则需要8或者10晶体管单元。低于0.5V时,Hou建议基于逻辑的存储器单元。

现在很难在某一次会议上听不到或者看不到关于物联网(IoT)和可穿戴式计算的讨论。但是,请读下去。当人们还在争论IoT设备5年内是会达到200亿规模还是40亿规模的时候,一个意外的挑战已经浮出水面。人们都认为市场上最新的半导体技术也是您下一设计最好的工艺技术。这种想法促进了IoT的雪崩式发展。

最近在硅谷举行的TSMC辅助支持系统论坛上清楚的阐述了这种发展。随着20、16和10 nm工艺的发展,最大的代工线负责人宣称,在老工艺尺寸基础上,不到5个低功耗新工艺代就回到了180 nm。为什么——为什么这么多?在小系统设计中,这些问题构成了新现实。

对电源的其他分析

并不是IoT发起了低功耗工作模式。多年以来,超低功耗微控制器领域就有此类产品。但是,大肆的宣传使得业界特别关注低功耗问题的两个方面:在很多IoT和可穿戴节点上以极低功耗可靠的工作,还有非常低的占空比。

极低功耗需求的来源不同寻常:能量收集。一些IoT设计人员并没有费劲的将电池装到极小的封装中或者难以企及的空间里,而是选择从节点环境中收集能量。他们使用了小型光电池,从周围光中收集能量,采用热电变换器转换浪费的热量,使用惯性发电机把运动转换为电流,还有一些其他手段。一般的结果是可靠的少量电源——至少结合了小的可充电电池和超级电容。

如果您能够将节点耗电保持在一定的功率预算范围内,从很实用的热电转换器的几百µW到光线暗淡的室内微小光电池的几个µW,那么这种策略避免了换电池等问题。

作为对比,较低的占空比并不是约束而是机遇。一般而言,距离数据中心越远,节点的大部分空闲的时间就越长。数据中心的目标应该是不低于80%的利用率。但是在今年的热点芯片大会上,ARM® CTO Mike Muller估计CPU浏览网页的平均工作时间是7%,MP3回放任务大约是3%。距离核心越远,IoT节点对空气温度进行周期性采样时,可能每小时只有几个毫秒在工作,占总时间的百万分之一。

很明显,低占空比应该是降低能耗的好机会。问题是怎么办。要解决这一问题,我们得回到工艺技术和超低功耗问题上。

研究占空比

在低占空比系统中,降低能耗(从而延长电池使用寿命)最高效的策略与您的老奶奶处理电费的策略一样:不使用时关掉它。但是这种好建议的背后却涉及到详细的规划和某些困难的决定。

关掉电源意味着将状态存储到非易失存储器中,除非您设计的节点不需要持续的状态信息就能够工作。但是保存状态需要花费时间和能耗,写入闪存会需要很大的突发能耗,这也要有大功率能源。因此,这并不总是可行的——特别是空闲时间很短或者不可预测的情形。在这些情形中,您可能需要保持数据的低功耗模式,包括在状态机中和在存储器中(图1)。这也是老节点及其大规模晶体管再次被关注的原因。

图1.不同的占空比强调了功耗的不同方面。

这些大规模晶体管内在的一个特性是低泄漏电流。如果您的服务器一直以fMAX运行,那么低泄漏并不是很重要,这是因为高速和低动态功耗并不是老工艺关注的重点。但是,如果您设计低占空比系统,大部分时间处于数据保持模式,您不得不延长小电池的使用时间,与动态功耗或者最初的性能相比,您更关心静态泄漏。

这一事实解释了为什么有太多的工艺选择。在180 nm,泄漏几乎没有,但是动态功耗相对较高,而fMAX较低。在28 nm,泄漏比较起来非常高——即使是TSMC针对28 ULP设计的改进型低泄漏晶体管,但是动态功耗和速度要好很多。您可以看一下您规划的占空比,选择您的工艺技术。

当然,并不会非常简单。在体系结构和实施的每一阶段,都会有一些因素影响占空比。例如,您可以禁止中断状态机或者ARM Cortex®-M0等极低功耗MCU,只中断主CPU,以处理触发了重要代码的关键事件。您可以选择无线网络,支持节点在大部分时间进入休眠状态,而不让它一直处于准备响应某一消息的状态。您可以使用硬件加速器来缩短占空比的工作部分。还可以把上游任务放到无线集线器或者云端。

相反,您也可以重新调整占空比。例如,可以放慢时钟以节省功耗,让任务非常慢的运行,从而不会进入休眠模式。或者,可以选择轮询节点,就像带着安眠药的夜班护士,让节点一直保持工作。

总之,要找到动态功耗、运行和空闲以及关断时间、工艺技术的最佳组合会是一件很难的事情。对于ARM的big.LITTLE多核CPU配置等方法,支持您在功能强大的内核中迅速运行较难的线程,然后对于后台任务,切换到较慢的低功耗内核。在某些点,您会有很多选择。

不论占空比还是处理器怎样安排,有一种策略具有明显的优势。对于静态和动态功耗,电压是公式中的二次项。如果您降低Vdd,fMAX就会下降,功耗也是如此。这一点解释了TSMC超低功耗产品的重要特性:其特性是能够工作在非常低的电压下,实际上,接近阈值。

近阈值挑战

据TSMC研发副总裁Cliff Hou,在0.7-0.5V范围内Vdd的准备过程需要很多工作。公司关注的是从高阈值晶体管中获得最佳性能。但是也要处理其他两个主要问题;时序变化和SRAM拓扑。

接近阈值工作的MOSFET驱动负载的时间要长一些。这一简单的物理现象将大部分处理器的时钟频率限制在1 MHz附近。但是,Hou指出还有另一个问题。他解释说,“接近阈值时,波形是非线性的。对此,需要调整静态时序分析,这样,芯片设计人员不用改变他们的方法。”

Hou说,对时序进行了很大的改动后,自然需要检查所有IP在接近阈值电平时能否正常工作。他报告说,“一般而言,检查进行的比较顺利。但是,我们注意到,某些单元——那些有三至四级的,使用了传输逻辑门的,在接近0.5V时会出现问题。”

SRAM有不同的问题:不同的电压电平需要不同的单元设计。一般具有读写辅助功能的SRAM单元在较高电压时能够很好的工作。但是接近0.5V时,则需要8或者10晶体管单元。低于0.5V时,Hou建议基于逻辑的存储器单元。

Altera 物联网 半导体 电流 电容 ARM Cortex MCU 电压 MOSFET 电路 Cortex-M0 相关文章:

- ALTERA FPGA在微处理器系统中的在应用配置(07-09)

- 藏在系统核心芯片中的DRAM控制器(12-10)

- 真实环境中的系统设计(09-09)

- 闪存革命无处不在(12-25)

- 悬崖边上的CPU设计师: 现在该往哪里去?(11-10)

- 可穿戴电子系统的发展——人类和嵌入式系统的结合(12-05)