IoT促进了低功耗的发展

时间:12-05

来源:互联网

点击:

走向极端

如果您决定降低Vdd,那么不用停在晶体管的阈值电压上。在亚阈值领域有很多逻辑设计,甚至是模拟设计。实际上,晶体管一直关断,您的电路通过调制泄漏电流来工作。自然的,这些逻辑能效非常高,但是非常慢。在TSMC论坛上,ARM的Muller认为这并不简单,在IoT环境中,重要的是在亚阈值工作。

Muller介绍了TSMC在未指定40 nm工艺上开发的测试芯片ARM,针对低电压进行了优化。芯片含有Cortex-A5和Cortex-M0内核,以及很多独立电源域,支持工程师针对各种近阈值和亚阈值策略进行试验,可以对各种处理器的各个部分进行不同的组合。

CTO对设计这类芯片提出了警告。他提醒说,您需要仔细的设计电平转换器,它承载了电源域和功率逻辑门开关之间的信号。这些器件必须在很宽的电压范围内高效的工作,电压范围非常宽以至于超出了逻辑晶体管的阈值范围。

在体系结构级,Muller指出关断内核与使其停留在数据保持模式有很大的不同。他说,80%的静态功耗来自SRAM。因此,减少工作周期之间必须要保持的有效状态非常重要。保持状态要消耗能量。

Muller说,使用传统的时序收敛方法也很难来管理时序。目前的时序工具假设延时主要来自RC。而这里时序的主要因素是电压栅极延时。Muller遗憾的指出,当您尝试实现时序收敛时,工具会把您带到错误的方向上。

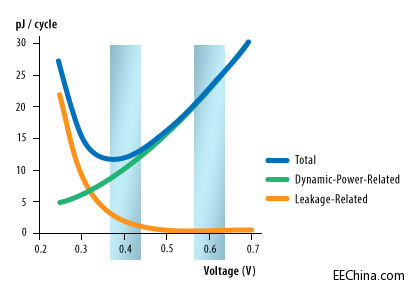

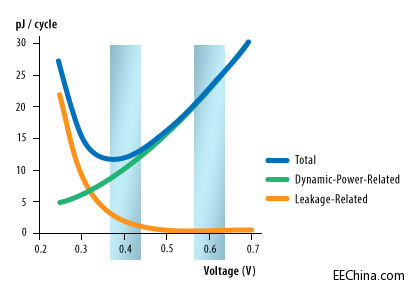

有了体系结构后,下一个问题是工作点。Muller针对这一主题提供了信息非常丰富的一幅图(图2)。Muller解释说,把Vdd降到阈值以下后,功耗——动态功耗和静态功耗,都下降了。在200 mV有最小功耗点,在此之下,电路会停止工作。如果您的电源受到高能耗器件的限制,那么这是最佳工作点。

图2.低于阈值电压时,每一任务的动态能耗继续下降,直至电路不工作,但是,随着电路变慢,由于泄漏导致的功耗在增大。因此,最小能量在最低功耗点之上。

但是随着功耗的下降,速度也在变慢。任务执行的时间越长,执行期间的静态功耗就越大。因此,您降低电压后,每一任务的总能耗并不会一直降低——实际上,有一个明显的转换点,电压低于这一点之后,每一任务的总能耗开始上升。在Muller的数据中,每一任务能耗达到最小的转换点是在400 mV。

Muller注意到,设计人员看到的曲线有很好的选择范围。如果功耗最重要,CPU可以工作在1 kHz,200 mV,功耗大约只有1 µW。如果目标是固定任务实现最低能耗,这一试验的最优点是在400 mV,100 kHz工作,功耗大约是100 µW。Muller总结说,“在600 mV近阈值区域,您不必要求功耗降低一半,设计会很容易进行。”

然而,重新进行设计并选择相应的电压还不够。在亚阈值区域,工艺变化和老化效应导致的阈值电压变化会非常严重。Muller介绍了亚阈值电路对于Vth非常敏感,在低占空比的低功耗电路中,偏置温度不稳定性(BTI)导致的微小漂移也会在很短的时间内造成电路失效。因此,设计人员必须仔细考虑其电路对各种变化的承受能力。

IoT节点对高能效的需求让我们费尽周折,从研究低占空比到深入研究亚阈值晶体管行为。现在,在成熟市场上,这些已经是常用的设计方法,其他的则留给博士们去研究。无生产线企业竞相进入可能空有承诺的IoT,所有这些选择具有连续性——完全不同的尺寸,以及多种工艺,设计人员可以从中选择他们的工作点。芯片设计人员的自由之处是能够向系统设计人员提出自己的要求,他们所面临的芯片规范与之前的大不相同,好在系统级还有机会。从长远看,近阈值和亚阈值方法仍然是IoT的主要方法。也是设计主流。

如果您决定降低Vdd,那么不用停在晶体管的阈值电压上。在亚阈值领域有很多逻辑设计,甚至是模拟设计。实际上,晶体管一直关断,您的电路通过调制泄漏电流来工作。自然的,这些逻辑能效非常高,但是非常慢。在TSMC论坛上,ARM的Muller认为这并不简单,在IoT环境中,重要的是在亚阈值工作。

Muller介绍了TSMC在未指定40 nm工艺上开发的测试芯片ARM,针对低电压进行了优化。芯片含有Cortex-A5和Cortex-M0内核,以及很多独立电源域,支持工程师针对各种近阈值和亚阈值策略进行试验,可以对各种处理器的各个部分进行不同的组合。

CTO对设计这类芯片提出了警告。他提醒说,您需要仔细的设计电平转换器,它承载了电源域和功率逻辑门开关之间的信号。这些器件必须在很宽的电压范围内高效的工作,电压范围非常宽以至于超出了逻辑晶体管的阈值范围。

在体系结构级,Muller指出关断内核与使其停留在数据保持模式有很大的不同。他说,80%的静态功耗来自SRAM。因此,减少工作周期之间必须要保持的有效状态非常重要。保持状态要消耗能量。

Muller说,使用传统的时序收敛方法也很难来管理时序。目前的时序工具假设延时主要来自RC。而这里时序的主要因素是电压栅极延时。Muller遗憾的指出,当您尝试实现时序收敛时,工具会把您带到错误的方向上。

有了体系结构后,下一个问题是工作点。Muller针对这一主题提供了信息非常丰富的一幅图(图2)。Muller解释说,把Vdd降到阈值以下后,功耗——动态功耗和静态功耗,都下降了。在200 mV有最小功耗点,在此之下,电路会停止工作。如果您的电源受到高能耗器件的限制,那么这是最佳工作点。

图2.低于阈值电压时,每一任务的动态能耗继续下降,直至电路不工作,但是,随着电路变慢,由于泄漏导致的功耗在增大。因此,最小能量在最低功耗点之上。

但是随着功耗的下降,速度也在变慢。任务执行的时间越长,执行期间的静态功耗就越大。因此,您降低电压后,每一任务的总能耗并不会一直降低——实际上,有一个明显的转换点,电压低于这一点之后,每一任务的总能耗开始上升。在Muller的数据中,每一任务能耗达到最小的转换点是在400 mV。

Muller注意到,设计人员看到的曲线有很好的选择范围。如果功耗最重要,CPU可以工作在1 kHz,200 mV,功耗大约只有1 µW。如果目标是固定任务实现最低能耗,这一试验的最优点是在400 mV,100 kHz工作,功耗大约是100 µW。Muller总结说,“在600 mV近阈值区域,您不必要求功耗降低一半,设计会很容易进行。”

然而,重新进行设计并选择相应的电压还不够。在亚阈值区域,工艺变化和老化效应导致的阈值电压变化会非常严重。Muller介绍了亚阈值电路对于Vth非常敏感,在低占空比的低功耗电路中,偏置温度不稳定性(BTI)导致的微小漂移也会在很短的时间内造成电路失效。因此,设计人员必须仔细考虑其电路对各种变化的承受能力。

IoT节点对高能效的需求让我们费尽周折,从研究低占空比到深入研究亚阈值晶体管行为。现在,在成熟市场上,这些已经是常用的设计方法,其他的则留给博士们去研究。无生产线企业竞相进入可能空有承诺的IoT,所有这些选择具有连续性——完全不同的尺寸,以及多种工艺,设计人员可以从中选择他们的工作点。芯片设计人员的自由之处是能够向系统设计人员提出自己的要求,他们所面临的芯片规范与之前的大不相同,好在系统级还有机会。从长远看,近阈值和亚阈值方法仍然是IoT的主要方法。也是设计主流。

Altera 物联网 半导体 电流 电容 ARM Cortex MCU 电压 MOSFET 电路 Cortex-M0 相关文章:

- ALTERA FPGA在微处理器系统中的在应用配置(07-09)

- 藏在系统核心芯片中的DRAM控制器(12-10)

- 真实环境中的系统设计(09-09)

- 闪存革命无处不在(12-25)

- 悬崖边上的CPU设计师: 现在该往哪里去?(11-10)

- 可穿戴电子系统的发展——人类和嵌入式系统的结合(12-05)