FPGA在电梯控制系统中的应用

摘 要: 介绍了基于Altera公司EP1K30TC144芯片的电梯控制器设计过程,描述了该控制系统的功能。该设计采用VHDL语言进行编程,以QUARTUSⅡ软件为开发平台,对本设计进行了仿真,并使用JTAG将程序代码下载到实验板上进行了硬件验证。

关键词: 电梯控制器; VHDL; EP1K30TC144; QUARTUSⅡ

随着社会的发展,电梯的使用越来越普遍,对电梯功能的要求也不断提高,相应地其控制方式也在不断发生变化。对于电梯的控制,传统的方法是使用继电器-接触器控制系统进行控制,进入全微机化控制的时代,微型计算机在电梯控制上的应用日益广泛。电梯的微机化控制主要有以下几种形式:①PLC控制;②单板机控制;③单片机控制;④单微机控制;⑤多微机控制;⑥人工智能控制。随着EDA技术的快速发展,CPLD/FPGA因其高速处理信号的能力、可在线编程、易于实现、开发周期短、便于维护等优点,使FPGA已广泛应用于电子设计控制的各个方面。本文就是使用一片Altera公司的EP1K30TC144为控制中心,以VHDL编程语言为基础进行了电梯控制器的设计,并做了仿真。

1 系统功能简介

电梯控制器[1]的功能:每层电梯入口处设有上下请求开关;电梯内设有乘客到达层次的停站请求开关;电梯所处位置指示装置及电梯运行模式指示装置;电梯每分钟升降一层楼。电梯到达有停站请求的楼层后,经过5 s电梯开门,开门指示灯亮,开门10 s后电梯门关闭,电梯继续运行,直到运行完最后一个请求信号后停在当前层;能记忆电梯内外所有请求信号,并按照电梯运行规则依次响应,每个信号保留至执行后消除。

电梯运行规则:遵循方向优先的原则,电梯上升时,只响应比电梯所在位置高的上楼请求信号,由下到上逐个执行,直到最后一个上楼请求执行完毕,如更高层有请求下楼信号,则直接上升到有下楼请求的最高层,然后进入下楼状态。电梯下降时,与上升状态规则相反。

输入信号定义:

系统复位信号:reset,高电平有效;

电梯入口处一层、二层的上楼请求开关:upone、uptwo;

电梯入口处二层、三层的下楼请求开关:downtwo、downthree;

电梯内部到达楼层的停站请求开关:one、two、three;

所有输入信号的规定为:1表示有请求,0表示无请求;

输出信号定义:

电梯外部上升和下降请求指示灯:lightup和lightdown,这些信号与upone、uptwo、downtwo和downthree信号相对应;

电梯内部乘客到达楼层的停站请求灯:arr,该信号与one、two和three相对应;

电梯所在楼层指示:p表示电梯在对应楼层;

电梯的运行状态:lightdown指示向下运行,lightup向上运行,arr指示电梯的开关门状态及是否到达楼层。

2 系统设计实现

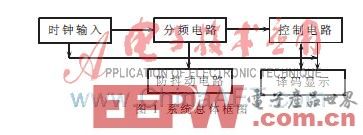

2.1 系统总体框图

系统总体框图如图1所示。

2.2顶层电路的设计

纵观各种基于FPGA的电梯控制器,很少有人介绍并使用构造体的结构描述方式。即在多层次的设计中,高层次的设计模块调用低层次的设计模块,或者直接使用门电路设计单元来完成一个复杂的逻辑电路的描述方法。结构描述方式最能提高设计效率,它可以将已有的设计成果方便地运用到新的设计中去。

本系统的顶层电路设计就采用构造体的结构描述方式。易于实现,易于纠错,易于修改程序。

上层模块源程序[4]及注释:

library ieee;

use ieee.std_logic_1164.all;

entity total5 is

port(uo,ut,dt,dth:in std_logic--一、二、三层楼电梯外的上下楼请求键。

o,t,th:in std_logic;--一、二、三层电梯里的按键。

pres:in std_logic;--reset信号。

clk:in std_logic;--时钟信号,1 MHz。

lightout:out std_logic_vector(6 downto 0);--数码管的输入信号。

lu,ld:out std_logic;--电梯上升,下降的灯。

arr:out std_logic);--开门的灯。

end;

architecture a of total5 is

signal templ0,templ2:std_logic;

signal templ1:integer range 3 to 1;

Signal

temp1,temp2,temp3,temp4,temp5,temp6,temp7:std_logic;

component bigmain--调用电梯控制模块。

port(upone,uptwo,downtwo,downthree

:in std_logic;

one,two,three:in std_logic;

reset:in std_logic;

clk,clk2:in std_logic;

p:out integer range 3 to 1;

lightup,lightdown:out std_logic;

arrive:out std_logic);

end component;

component fangdou --调用防抖动模块。

port(clk:in std_logic;

key:in std_logic;

keyout:out std_logic);

end component;

component fenpin--调用分频器模块。

port(clk:in std_logic;

clk1,clk2:out std_logic);

end component;

component display--调用译码显示模块。

port(clk :in

- ALTERA FPGA在微处理器系统中的在应用配置(07-09)

- 藏在系统核心芯片中的DRAM控制器(12-10)

- 真实环境中的系统设计(09-09)

- IoT促进了低功耗的发展(12-05)

- 闪存革命无处不在(12-25)

- 悬崖边上的CPU设计师: 现在该往哪里去?(11-10)