HPI接口在TI DSP中的应用及常见问题分析

简介

HPI接口是TI为处理器之间直接互连通讯定义的一种异步接口,大多数TI DSP芯片上都有HPI接口。HPI接口是从(Slave)端口,接在主机的扩展内存总线上,DSP不能通过HPI向主机(Host)的访问,只能被主机读写。两个DSP的HPI接口之间不能通讯。两个DSP之间互连,可以将一个DSP(从)的HPI接到另一个DSP(主)的扩展内存接口(EMIF)上[1].

1. HPI工作模式

不同系列DSP上的HPI接口版本有所不同,区别体现在DSP对HPI的控制上,如C6727上的UHPI可通过寄存器使能与关闭HPI接口,对主机访问DSP内存空间的控制,以及对HPI接口信号的功能复用上。但从主机访问的角度,HPI的工作模式分为:复用模式(Multiplexed-Mode)和非复用模式(Non-multiplexed-Mode)。

复用模式下没有地址线,主机访问DSP的地址信息是以数据方式送到HPIA(HPI地址寄存)。从硬件信号的角度,地址,数据信号是由同一组数据线传递,所以称为复用模式。

非复用模式的数据线与地址线是分开的,与内存接口连接相似。非复用模式不需要操作HPIA寄存器,主机访问的地址信息通过地址总线直接送给HPI.

所有的HPI接口都支持复用模式,但不是所有芯片的HPI接口都支持非复用模式(参考相应的芯片手册确定是否支持)。除了有无HPIA的操作区别外,两种模式的操作没有区别。因为非复用模式的操作是复用模式操作的子集,为方便起见,本文以复用模式展开讨论。

2. HPI硬件信号连接

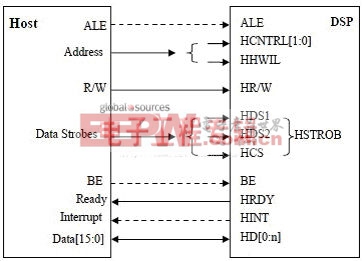

HPI接口复用模式连线如图1所示,根据在应用当中的必要性分为:必要的,和可选的两组信号。可选的信号以虚线表示。

图1:HPI接口复用模式硬件连接

●数据线HD[0:n]:在复用模式下,数据线的宽度一般为CPU位宽的一半,一个HPI访问分为高低半字的两次访问,如C5000 是16-bit CPU,HPI数据线为8位,C6000 是32-bit CPU,其HPI数据线为16位。C64x系列的HPI支持32位,在32位模式下一个HPI访问不需要分为高低半字两次访问组成一个完整的访问。

●HCNTL0/1,HWIL:HCNTL0/1 选择要访问的HPI寄存器,HWIL控制访问寄存器的高低半字,必须先高后低。一个寄存器的高低半字的两次访问一定要连续完成,中间不能插入其它的HPI操作。只有HPIC可以只访问半个字。

●HR/W:指示对HPI寄存器进行读,还是写操作。如果主机的读,写信号是分开的,可以利用其中一个信号,但要注意做上拉或下拉处理以控制其在三态时的电平。

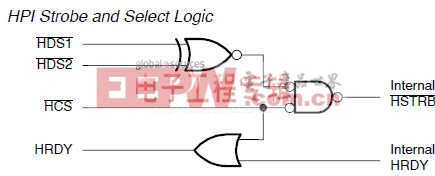

●HCS,HDS1/2:这三个信号根据图2 的逻辑产生内部HSTROBE 信号,其逻辑关系是要求HDS1 和HDS2信号相反,HCS低有效。HSTROB下降沿的时间点反应的是三个信号中最后跳变的信号。HPI 在HSTROB的下降沿采样控制信号HR/W,HCNTL0/1,HWIL 以判断主机要对哪个寄存器进行读,或者写操作命令。

注意控制信号在HSTROBE的下降沿之前需要最少5ns 的setup稳定时间,而HDS1/2和HCS 到HSTROBE信号内部门电路的延时是皮秒级的,所以控制信号的setup时间需要外部时序保证。

图2:HSTROBE信号产生逻辑

●HRDY:HPI的输出信号,指示当前操作状态,用做硬件流量控制握手信号。

●HINT:通过HPI,主机与DSP之间可以互发中断。HINT是HPI送给主机的中断信号,DSP对HPIC[HINT]位写1,HINT信号线上送出高电平信号,主机可利用此信号做为中断信号输入。DSP不能清除HPIC[HINT]状态,主机在响应中断后,需要对HPIC[HINT]位写1清除状态,DSP才能再次对HPIC[HINT]置位发中断。主机通过写HPIC[DSPINT]置1给DSP产生中断,DSP在响应中断后,需要对HPIC[DSPINT]写1清除状态,主机才能继续操作HPIC[DSPINT]给DSP发中断。通过HPI传输数据,结合互发中断做为软件层的握手信号,可有效提高通讯的效率与灵活性。

●ALE:存在于地址,数据线复用的主机上用来指示地址信号周期,这种总线复用的主机很少见,所以通常将ALE固定上拉处理,只用HSTROBE采样控制信号。

●BE:Byte Enable信号,这个信号只出现在32位的C6000 DSP上。因为应用当中通常都是对整个32-bit字进行访问,所以直接做上拉使能处理。

3. HPI寄存器地址映射

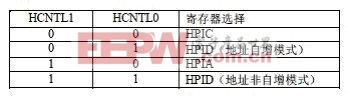

HPI口提供给主机端访问的寄存器只有4个,通过HCNTL[1:0]选择。

表1:HPI寄存器访问选择

由于在复用模式下数据线通常只有寄存器宽度的一半,所以一个完整的数据访问由高低半字两次访问组成,由HWIL信号控制,HWIL信号必须是先低后高。通常将HWIL和HCNTL[1:0]接在主机的地址线上,将4个寄存器映射为主机端的8个内存单元,下表中的地址线连接方法将8半字寄存器映射到主机的8个连续的内存单元。这里的地址线是用来选择HPI的寄存器,与非复用模式下的地址线直接访问DSP的内存空间是完全不同的作用。

表2:HPI

- 基于DSP的HPI接口的视频数据传输系统设计(03-01)

- 处理器的HPI接口与PCI总线接口设计(02-11)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)