基于DSP的HPI接口的视频数据传输系统设计

引 言

在视频监控、远程视频播放等系统中,通常需要将视频图形数据通过网络传输到远程处理机上。作为数字信号处理专用处理器,DSP虽然在视频压缩等方面有很大的优势,但对诸如任务管理,网络通信等功能的实现较困难。运行于通用嵌入式处理器的Linux操作系统,开源,可以根据需要修改内核,支持各种网络协议,并且其任务调度机制性能卓越。综合二者的优点,嵌入式视频平台可以由DSP完成图形处理功能,并通过高速接口把视频数据传输给嵌入式微处理器,然后由嵌入式Linux系统完成网络传输功能。

目前DSP与微处理器之间的高速通信方式有以下几种:共享内存,此种技术对软硬件的设计要求都非常高,同样效率也最高;通用高速总线接口,如PCI、 USB等,这种类型的通信方式采用复杂的链路协议,软件设计困难;专用接口,如TI公司DSP提供的HPI(Host Port Inter-face)。本文研究了TMS320E)M642的HPI接口,并提出一种在TMS320DM642和AT91RM9200间高速通信的软硬件实现方案。通过HPI接口,TMS320DM642可以高速地将实时视频数据传输给AT91RM9200;在AT91RM9200上,Lnux驱动实现存储器映射I/O和物理内存重映射,避免了视频数据在应用程序与内核之间的二次拷贝,提高了应用程序的网络发包效率。

1 HPI接口硬件设计

HPI是一种并行接口,支持32位(HPl32)和16位(HPll6)数据总线,通过HPI的数据寄存器(HPIDA、HlPIDF),ARM可以间接存取DSP的存储空间。在DSP内部,数据从存储单元到HPI数据寄存器的传输,是由EDMA(增强DMA)控制器完成的。

HPI控制器的外围引脚包括HD[0-31]、数据总线。HCNTL[O-1]是寄存器访问控制线,HPI控制器有4个寄存器,通过这两根控制线,DSP 可以确定ARM要访问的寄存器。其中,HPIA地址寄存器,存放当前访问单元的地址;HPIC为控制寄存器,实现各种控制命令;HPIDA自增长数据寄存器,每访问一次该寄存器HPIA的内容加4;HPIDF固定地址数据寄存器,与HPIDA不同之处在于,访问该寄存器后HPIA的内容不变。HHWIL,高低位访问控制线,它只用于HPll6模式中,该控制引脚决定寄存器的高或低16位被主机访问。HR/nW,HPI控制器4个寄存器的读写控制线。 HDSl、HDS2和HCS,其中HDSl、HDS2可连接ARM的读、写控制线,HCS连接ARM的nCS7片选线,三者在DSP内部组合形成一个 HSTROBE信号,当HCS低有效并且HDSl或HDS2的读或写低有效,决定数据寄存器(HPIDA、HPIDF)的读或写操作。HAS,地址锁存线,当主机的地址线与数据线复用时,主机可用该控制线通知。DSP锁存地址;其他不用该控制线情况时,应接高电平。nHRDY,DSP输出线,表示HPI 总线是否可访问。nHINT,中断输出线,用于中断ARM。

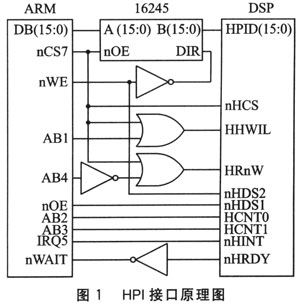

DSP与ARM接口电路如图1所示。采用HPI16模式,16根数据线通过16245数据隔离器接到ARM数据总线的低16位,将HPI的片选空间置于 ARM的nCS7片选线上,HR/nW读写信号经反向器接到ARM的AB4地址线,HCNTL[O-1]与ARM的地址线AB[2-3]相连,则HPI的 4个寄存器的读基地址为0x80000000,写基地址为0x80000010。在ARM端从这两个地址开始访问,相应地对HPI 4个寄存器访问。

ARM通过HPI读写DSP数据空间,须按以下三步顺序执行:首先,对HPIC寄存器初始化,主要针对HPI16模式最低位HWOB位设置,决定数据传输格式是按高半字在前(设置为0),还是低半字在前(设置为1),该位对于HPI32模式无效,可不设置;然后,对HPIA寄存器初始化,设置访问单元的地址;最后通过读写数据寄存器(HPIDA、HPIDF)实现数据读写操作,其中读写HPIDA寄存器是完成连续地址单元读写操作,读写HPIDF寄存器是完成固定地址单元读写操作。注意,在ARM读写的过程中,如果DSP的nHRDY控制线一直为高,表示HPI数据总线未准备好,ARM的读写操作必须等待;当nHRDY为低后,ARM才继续向下执行指令。

2 Linux驱动设计

Linux虽然是一种整体式操作系统,但允许在运行时动态加载或删除功能模块。这个特点方便了驱动功能模块的开发。Linux系统支持两种模块调用方式:一种是静态编译,直接编译进内核,在系统启动时就运行;另外一种是动态加载,在内核运行时,用insmod/rmmod实现模块的加载和删除功能。在嵌入式系统开发中,一般采用动态加载方式,避免了系统频繁重启。当最终发布产品时,可以把模块直接编译进内核。这种处理方式比较简单,且效率高。

Linux系统中,内存地址主要涉及以下几个概念:物理地址、内核虚拟地址(包括内核逻辑地址)和进程虚拟地址。在内核层,当内核要访问某内存空间时,用的是内核虚拟地址,再由MMU(存

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)