处理器的HPI接口与PCI总线接口设计

1 HPI接口功能及特点

主机接口HPI(Host Pott Interface)是C54x DSP系列定点芯片内部具有的一种并行接口部件,主要用于与其他总线或CPU之间进行通信,其接口框图如图l所示。主机是HPI口的主控者,HPI口作为一个外设与主机连接,使主机的访问操作很方便。主机通过以下单元与HPI口通信:专用地址和数据寄存器、HPI控制寄存器以及外部数据和接口控制信号。HPI有两种工作方式:共用寻址方式(SAM)和仅主机寻址方式(HOM)。在SAM方式下,丰机和C54x都能寻址HPI存储器;在HOM方式下,仅能让主机寻址HPI存储器,C54x则处于复位状态,或者处在所有内部和外部时钟都停止工作的IDLE2空闲状态(最低功耗状态)。

VC5402是TI公司推出的一款性价比极高的16位定点处理器。它是C54x系列中应用比较广泛的一种芯片,有着丰富的接口资源,是一种集数据处理和通信功能于一体的高速微处理器。VC5402 HPI口是一个增强的8位主机接口,它通过HPI控制寄存器HPIC、地址寄存器HPIA和数据锁存器HPID来实现与主机之间的通信。主机通过外部引脚HCNTLO和HCNTL1选中不同的寄存器,则当前发送8位数据就到该寄存器。控制寄存器HPIC既可以被主机直接访问,又可以被DSP片上CPU访问。在使用上,由于主机接口总是传输8位字节,而HPIC是一个16位寄存器,所以主机向HPIC写数据时,需要发送2个相同的8位数据。地址寄存器HPIA,只能被主机直接访问。主机将HPIA寄存器视为一个地址指针,借助于HPIA主机可以访问VC5402全部的片上存储器。另外HPIA具有自动增长的功能,在自动增寻址模式下,一次数据读会使HPIA在数据读操作后增加1,而一个数据写操作会使HPIA操作前预先增加l。这样如果使能了该功能,则只须设定一次HPIA即可实现连续数据块的写入和读出。数据寄存器HPLD,只能被主机访问。如果当前进行的是读操作,则HPID中存放的是要从HPI存储器中读出的数据;如果当前进行的是写操作,则存放的是将要写到HPI存储器的数据。

2 VC5402的HPI口与PCl2040的接口设计

2.1 PCI总线及其实现方法

PCI局部总线是32或64位数据总线,32位PCI总线在读写传送中支持132Mb/s的峰值传送速率,64位PCI传送支持264Mb/s峰值传送速率。对于64位66MHz的PCI总线,传送速率可达528Mb/s。PCI总线协议规范复杂而庞大,因此需要借助总线接口来实现。实现PCI总线协议一般有两种方法:一是用FPGA设计实现,但PCI协议比较复杂,因此难度较大;二是采用PCI总线控制芯片,如AMCC公司的S5933和PLX公司的PCI9052等通用的PCI接口芯片。TI公司专门推出了针对PCI总线和DSP接口的芯片PCI2040,它不但实现了PCI总线控制的功能,而且提供了和DSP芯片的无缝接口,因而大大降低了系统设计的复杂度,缩短了开发时间。

2.2 P012040与DSP接口设计

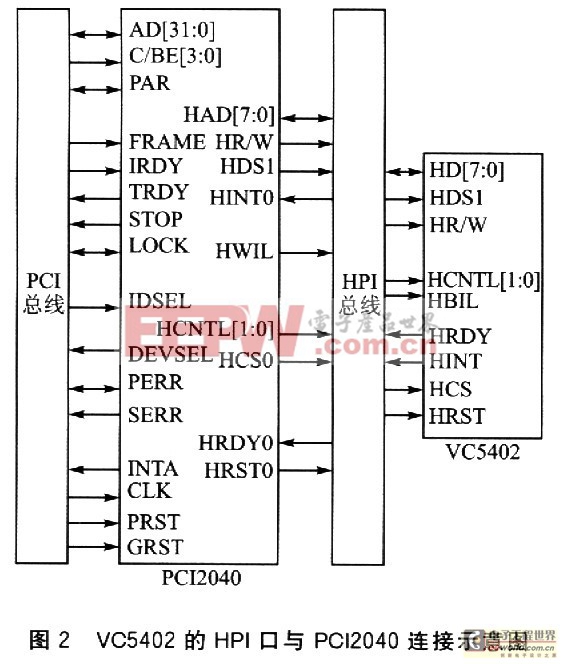

PCI2040足TI公司设计的专门用来实现C5000/C6000系列DSP和PCI总线进行接口的专用芯片,可以通过8位或16位HPI接口与C54x/C6xDSP实现无缝连接。PCI2040通过HPI接口与VC5402连接。PCI2040的HPI口为8/16位数据传输接口(8位还是16位,依据所挂接的DSP的类型)。主机作为传输的主设备,从机DSP不能发起传输。主设备PCI2040可以读/写DSP内存,DSP HPl口可以访问DSP所有的片上资源,PCI2040和VC5402之问的通信主要靠DSP的HPIA、HPIC、HPID三个寄存器完成。VC5402的HPI与PCI2040口的连接如图2所示。

PCI2040的数据总线HAD0~HAD7与VC5402 HPI口的数据总线HD0~HD7相连,用于主机和DSP传输数据。PCI2040芯片的HPI口的HCNTLl和HCNTL0引脚分别与DSP的HCNTLl和HCNTL0引脚相连,以实现其对HPI寄存器的访问。具体HPI寄存器的选择和访问模式的确定由DSP的HCNTLl和HCNTL0引脚的状态决定,表1给出了VC5402 HPI寄存器访问控制的情况。PCI2040带有独立的读/写选通信号HDS和HR/W,可以将PCI2040的HDS、HR/W引脚与VC5402的HDSl、HR/W引脚相连,实现主机对VC5402 HPI接口的读/写控制。当主机驱动HR/W为高时,

TMS320VC5402 HPI接口 PCI总线 相关文章:

- 基于DSP CCS 2.2实现指纹识别预处理系统(07-28)

- TMS320VC5402 DSP与单片机的HPI接口实现 (09-30)

- 基于DSP TMS320VC5402的水表号码图像采集系统的研究(10-29)

- 基于HPI方式自举在TMS320VC5402 DSP芯片上实现(05-29)

- TMS320VC5402 I/o资源配置及与USB通信(10-04)

- PC/104总线与HPI口通信的解决方案(12-21)