TMS320VC5402 I/o资源配置及与USB通信

引言

DSP(数字信号处理器)芯片TMS320VC5402具有高性能、低功耗、资源多等特点,其独特的6总线哈佛结构,使其能够6条流水线同时工作,工作频率达到100 MHz。具有2个缓冲串口BSP、8位并行EHPI(增强主机接口)、可编程的等待状态发生器等,可以满足数据处理控制的要求。

针对此应用系统通信接口数据量大、对速度要求高、实时控制的特点,本项目采用高速USB(通用串行总线)接口实现了高速的数据处理与传输。USB是一种新型接口技术,是计算机和外围设备接口通信的一种总线标准。它支持热插拔、即插即用,连接简单。本文将介绍VC5402的GPI()(I/0)资源配置及CY7C68013与外设的从(Slave)FIF0接口方式。

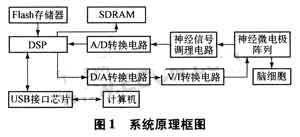

1系统原理

本系统以TI公司的TMS320VC5402 DsP为主控制器,主要分为神经信号处理电路、神经刺激电路和信号传输电路3部分。系统首先根据相应的控制信号选通神经微电极阵列的某路或多路测点,发出相应的刺激信号,并在对脑细胞进行电刺激的同时记录细胞反应,并将采集到的神经信号数据通过USB口传送到上位机,进行病理分析,从而实现了对电刺激的控制和脑信号的高速实时传输和处理。该系统可根据所建的脑电信号数据库,模拟产生与运动相应的神经信号,分别对不同的脑区域进行电刺激,达到治疗的目的。系统方案如图l所示。

TMS320VC5402除了使用VC54x系列中常用的GPIO外,还为用户提供了多个可选择的GPIO:HPI一8和McBSP。可与各类存储器直接接口。

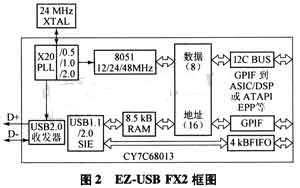

USB2.0控制器选择Cypress公司的FX2系列产品cY7C68013。EZUSB FX2是Cypress公司生产的世界上第1个USB2.0的集成微控制器,包括1个805l处理器、1个SIE(串行接口引擎)、1个USB收发器、8.5 kB片上RAM、4 kB FIF0存储器和1个GPIF(通用可编程接口),总线标准传输速度达480 Mbit/s,足够满足高速外设的速率要求。其结构如图2所示。

2 TMs320VC5402 I/o资源配置

由于本系统含有多个处理模块,而且在同一时刻,神经微电极阵列要选通多路同时进行神经电刺激、信号采集及USB传输。DSP芯片的GPIO资源不够用,需要扩展I/0以满足需求。因此,本项目将EHPI配置为8位通用I/O,用做数据线与cY7C68013通信。将McBSP配置为通用I//0,用做CY7C68013的控制线。

2.1 EHPI-8用做GPIO

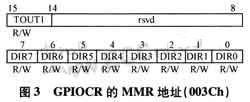

FMS320VC5402的8位EHPI将DSP设置为从模式来完成与主处理机之间的通信任务,使得主机和DSP均可以访问DSP上存储器。但HPI.8的8位双向数据总线也可以用做GPIO引脚。这个功能仅当HPI-8接口禁止时有效,即当HPIENA引脚在复位过程中被置为低电平时有效。可通过GPIOCR(通用输入/输出控制寄存器)和GPIOSR(通用输入/输出状态寄存器)这两个存储器映射寄存器用来控制HPI.8数据引脚的GPIO功能。

GPIOCR的方向位(DIRx)用来设置HD0~HD7是输入还是输出。如图3所示。定时器1输出位TOUTl只对那些有两个定时器的器件才有效,它控制定时器l输出到HINT引脚上。当系统只有1个定时器时,该位被保留。当HPI一8接口使用时,TOuTl位和DIRx为被强迫置零,并且通用输入/输出引脚只能处于输入模式。

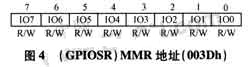

GPIO引脚(HDx,x=0:7)的状态可以用GPIOSR中的位来监控。如图4所示。当一个HDx引脚被设定为输入端时(通过对GPIOCR中的DIRx位写入一个"O"),GPIOSR中对应的位可以被读取以确定这个引脚上探测到的逻辑值。同样,当一个HDx引脚被设定为一个输出端时,驱动到这个引脚上的逻辑值被写人GPIOCR中的相应位。

要把HPI一8的数据引脚当做GPIO引脚使用,首先要对这些引脚进行适当的设置,然后可以通过读写GPIOSR来监控或操作这些引脚。

2.2 McBSP用做GPIO

TMS320VC5402是54x系列中最早引入McBSP(多通道缓冲串行口)的芯片。该串行口在以下两个条件成立时(串口引脚CLKX、FSX、DX、CLKR、FSR和DR可以被用作GPIO引脚,而不作为串口引脚):

a)串口的相关部分(发送端或接收端)处于复位状态,即SPCR[1,2]中

b)串口的相关部分的GPIO引脚功能被启用,即PCR中的(R/X)IOEN=l。

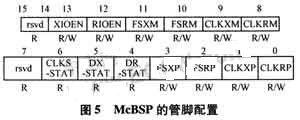

PcR(引脚控制器)说明了将McBSP的引脚配置成通用I/0引脚的位,如图5所示。

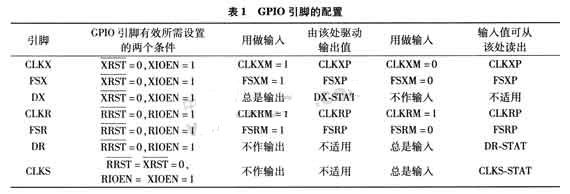

表l列出了详细的配置情况。

以Fs(R/x)为例,Fs(R/x)M=0设置该引脚为输入,而Fs(R/x)M=l则设置该引脚为输出。当FS(R/x)配置为输出时,驱动到FS(R/x)引脚上的值是存储在Fs(R/x)P中的值。如果Fs(R/x)配置为输入,那么Fs(R/x)P变为只读位,它反映Fs(R/x)信号的状态。类似地,CLK(R/x)引脚也可由CLK(R/X)M和CLK(R/x)P如此配置。

DX总是用做输出,当发送端被选做GPIO引脚时,PCR中DX-STA3、位的值被驱动到DX上;DR总是作为输入,并且它的值保存在PCR的DR.

TMS320VC5402 I O 资源配置 USB通信 相关文章:

- 基于DSP CCS 2.2实现指纹识别预处理系统(07-28)

- TMS320VC5402 DSP与单片机的HPI接口实现 (09-30)

- 基于DSP TMS320VC5402的水表号码图像采集系统的研究(10-29)

- 基于HPI方式自举在TMS320VC5402 DSP芯片上实现(05-29)

- PC/104总线与HPI口通信的解决方案(12-21)

- TMS320VC5402与单片机的HPI口通信设计(02-07)