8051 与 AndesCoreTM 的软件差异与移植

表的例子中,我们需要将中断向量表最终设定在 0 地址处,可以通过 section 语法配合 sag 工具实现,例子中我们设定 该段 的 section 名为 .vector, 所 以在 sag 中 ,我 们自 定义一个 USER_SECTION 为.vector,并将.vector 放在 0 开始的地方并作为第一个 section。

| USER_SECTIONS .vector SDRAM 0x00000000 0x00800000 ; address base 0x00000000, max_size=8M ;指定 LMA 为从 0 开始 { EXEC 0x00000000 ;指定 VMA 为 0 { * (.vector) ;放在 0 开始的地方并作为第一个 section * (+RO,+RW,+ZI) STACK = 0x00800000 } } |

通过上面的 sag 语法,并使用 andes 提供的 sag 转 ld 的工具,可以产生类似以下的 ld,在工程进行链接的时候选择该 ld 时就能确保 .vector 链接的地址位 于 0 处。

| /* This file is generated by nds_ldsag (version 20140127). */ ENTRY(_start) SECTIONS { PROVIDE (__executable_start = 0x00000000); NDS_SAG_LMA = 0x00000000 ; SDRAM_BEGIN = NDS_SAG_LMA; . = 0x00000000; ; 起始地址为 0 .vector : { *(.vector) } ; .vector 在 0 开始的位置 .nds32_init : { KEEP(*(.nds32_init)) } .interp : { *(.interp) } .hash : { *(.hash) } .dynsym : { *(.dynsym) } .dynstr : { *(.dynstr) } .gnu.version : { *(.gnu.version) } ...... |

关于详细的 SAG 使用,可以参考我们的另一篇文章:《Andes 的分散聚合(SAG)机制》http://www.andestech.com/cn/news-events/technical-article/2014/Andes20141008.pdf

5.2. 中断处理函数的 C 实现

[8051]

怎样用 C 写 8051 的中断处理函数范例

| /* com interrupt handler */ void com_int(void) interrupt 4 // 有指定 interrupt 号 { /* com interrupt handler here */ } |

[AndesCore?]

怎样用 C 写 AndesCore?的中断处理函数范例

| void syscall_handler() // 和普通函数的写法相同 { puts("this is syscall handler\n"); } |

6. 适用于 MCU 的 Andes CPUs

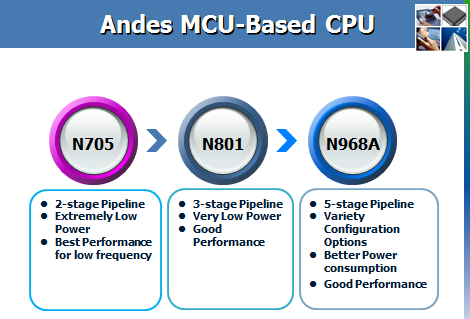

Andes 有三款非常适用于 MCU 应用的 CPU,分别是:N705,N801,N968A,如 下图所列:

N705 和 N801 分别采用了两级和三级流水线,都具有很低的功耗和很好的性 能,当应用需要的频率较低时,使用两级流水线的 N705 能发挥出更好的性能和 更低功耗的特性,相比于 8051,两级流水线的 N705 在频率方面高出许多,比 如在 TSMC 40nm LP 工艺下能跑到超过 240MHz,所以完全能胜任 8051 的应 用需求。N968A 使用了五级的流水线,同样有低功耗的特性和很好的性能,同 时该款 CPU 具有很强的可配置性,如支持多种总线接口,还支持了专门为 audio 的加速指令,N968A 是一个多面手,性能好,功耗低,又具备强大的可配置特 性,适合于多种应用。

7. 总结

AndesCore?使用标准的 C 语法开发,方便快捷,同时作为 32 位 RISC(精 简指令集)架构的 CPU,AndesCore?有多款适用于 MCU 应用的 CPU,相对于8051 具有功耗,性能方面优势。想了解更多 AndesCore?细节,可以登陆www.andestech.com。

andes andescore 8051 MCU 相关文章:

- EDM安全访问机制应用方案(02-12)

- 在晶心平台运行具 OSC 的 FreeRTOS(01-08)

- Andes SAG应用实例(12-04)

- Andes 的分散聚合(SAG)机制(09-22)