在晶心平台运行具 OSC 的 FreeRTOS

晶心科技设计 IP 的目的,是满足客户实际需求,提供低功耗高效率的产品 给客户,让客户可以做出极具竞争力的 SoC,达到客户与晶心科技双赢的目的, 本文介绍具 OSC 的 FreeRTOS 产品,巧妙地与 AndesCore?结合,客户导入产品 后,具竞争力与实用性,本文的目的是期望能够让更多的读者清楚这个产品的特 性与优势进而使用此产品。

某些电子产品的应用是不同的时间需要运行不同的功能,这时需要大空间的 ROM 与 RAM 来存放在运行时会用到的各式各样的功能。因为 CPU 同时间只 会运行一种功能。所以在务实与经济的考虑下可以使用 overlay 的方式来满足此 类型产品的需求,将大幅降低 RAM 空间的使用,让硬件成本降低,使得产品竞 争力大大的提升。达成 overlay 的方式有两种,纯软件 overlay 与硬件加速 overlay。 纯软件的 overlay 不需增加硬件,但软件工程师写程序时需自己配置 functions 摆 放的位置,容易出错;呼叫 functions 时需要经过额外的处理,降低程序效能。 因此纯软件的方法多用于只需偶尔更换 overlay 的应用。例如 audio player,一条 歌播完,下一条开始前,才需要检查是否要用不同 decoder。我们有另一篇文章 针对软件 overlay 做介绍,本文不多加探讨。

硬件加速的 overlay 使用少许硬 件 , gate count < 2K (OSC, Overlay SRAM Controller),提供软件透明的 overlay 处理。软件工程师写程序时,可以假设有一 个很大的连续程序空间,完全不需配置 functions 摆放的位置,这大大增加开发 程序的效率;同时,呼叫 functions 时完全没有任何纯软件方式的 overhead。上 述之 OSC 优点可以符合客户这类的需求,如果客户系统复杂,要做的事比较多, 需要用到多任务(Multi-tasking),则晶心科技「支援 OSC 的 FreeRTOS 产品」 就是最佳解方案。

1. Andes OSC 工作原理

先设定AndesCore? NCEOSC100 IP中寄存器,再与运行软件做整合搭配, 即可执行OSC的功能。

1.1 设定 OSC IP 的寄存器与动作解说

■ OSC Control Register, OSCCTRL (+0x00)

■ OVL_SZ: 3’h4 (16KB) RO/WI

■ OVL_VALID: 0

■ Fixed Region Size Register, OVLFS (+0x04)

■ OVL_FSZ: 8’h18 (96KB) RW

■ Overlay Region Base Register, OVLBASE (+0x08)

■ Overlay Region End Register, OVLEND (+0x0C)

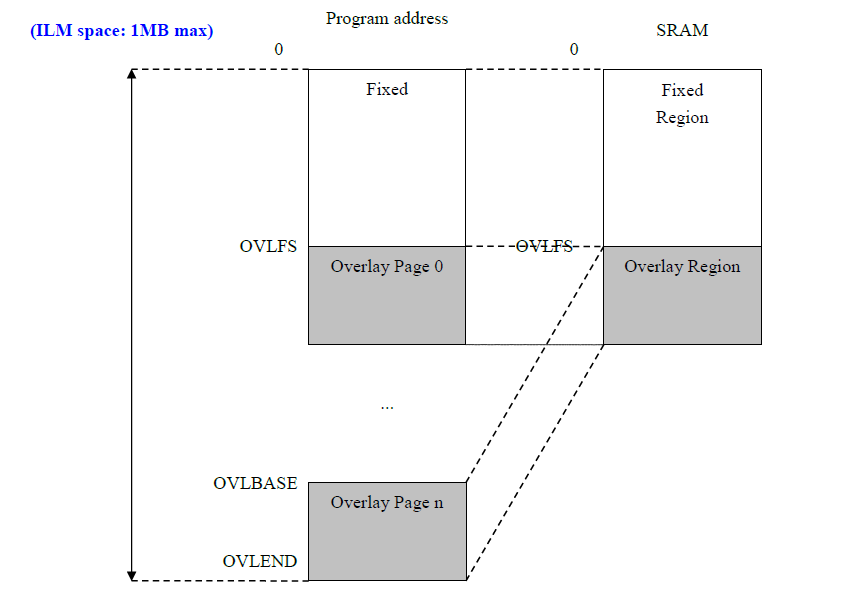

在OSC设计中SRAM分为两个区域,一个是”fixed region” ,另一个是 “overlay region”,fixed region 为低地址的 SRAM ,其大小由OVLFS 寄存器设 定。 overlay region 是一个动态的区域,其地址由OVLBASE寄存器设定,大小 由 OVL_SZ 设定。当CPU运行时存取地址落在寄存器 OVLBASE与OVLEND之 间时OSC将自动转址到SRAM的overlay region内,如图1所示。

因应实际需求设定多个Overlay 区域,当发 生 ”Overlay Miss” 时 ,经由 Overlay Exception的机制与软件的搭配,可以将storage 中的 overlay page N 复 制到 SRAM 中的Overlay Region,如图1所示。关于overlay page 置换的工作原 理将于下两个章节中做说明。

图 1. Overlay 范例说明

CPU运行时存取地址不在fixed region 或是当时有效的 overlay page 时,会 发生 Overlay Miss 。当 Overlay Miss 发 生时 OSC 会产 生 illegal instruction (32’hcoddcodd)造成general exception。因为也有其他原因会产生general exception, 如何区分出overlay miss 与其他general exception,将于下个章节说明。

1.2 Overlay Exception 侦测

当进入 general exception 时可透过软件检验下列程序来判断是否为overlay miss:

Step 1 如果 interrupt level 已经到达最大值 (PSW.INTL == Max INTL) ,这是 fetal error 不是overlay miss。

Step 2 必须是ITYPE.EYPE==1,才有机会是overlay miss。

Step 3 检查IPC值,如果是落在fixed region 或是当时有效的 overlay page 时 这是真 正的 illegal exception case. 如果 不 是在这 两个 区域 则是 overlay miss。

经过前面3步骤验证,如果确定是overlay miss ,则可进行Overlay exception handling 的动作。

1.3 执行

andescore soc 晶心科技 freertos 相关文章:

- EDM安全访问机制应用方案(02-12)

- 8051 与 AndesCoreTM 的软件差异与移植(07-29)

- IP核在SoC设计中的接口技术 (08-06)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- Linux下Sniffer程序的实现(06-12)