视频并行处理系统分析与设计

摘要:视频数据处理的特点是数据量大,而且各种视频处理模块的数据交换频繁,实时性要求高。为了满足海量视频数据的处理,提出了一种利用非透明桥连接多个CPU桥连的硬件架构及其并行处理方法,实现视频的并行处理。本系统突破了单个高性能CPU的计算能力,大大提高了海量视频信号的处理能力;而且该处理方法不会单纯地依靠硬件技术如CPU处理速度等的发展,可以通过合理调节视频处理步骤来实现快速视频处理的功能。

引言

图像与人们的生产生活息息相关,是人类获取和交换信息的主要来源,据统计人类有80%以上的信息来自于图像。随着数字化进程的加速普及,人们对视频的需求提出了更高要求,电视、内容、数字 摄像机等提供的各种形式视频正在向高清转变。高清晰度的视频在各个领域的应用越来越广,3D技术也日趋成熟,需要对海量视频数据进行复杂处理的应用越来越多,这对视频处理技术提出了一个新的挑战。传统的视频处理多采用GPU( Graphic Processing Unit图形处理器)进行,限于目前单个显卡的处理能力有限,需要同时对一个大屏幕的高清视频数据进行纹理映射、颜色混合、3D渲染等操作的场合已经很难胜任了。近年来,对于视频并行运算的研究取得了很多进展,提出了很多的解决办法,但是这些办法都是仅仅解决了视频处理中的某一个问题。例如目前利用网络进行并行运算的计算机系统,虽然其并行运算的能力较强,但是对于海量的视频数据,其数据传输能力有很大的局限性;网络带宽不足以实时地传输信号,这导致出现图像无法流畅显示的问题,随着目前需要处理的视频数据量的增加,这种缺陷已越来越严重。

1 非透明桥技术

非透明桥顾名思义是一座连接两端处理器的桥梁,且两端的处理器均有独立的地址空间,桥两端的主机不能看到另外一个主机完整的地址或者I/O空间。 在非透明桥环境中,PCI Express系统需要在从一个内存地址空间穿越到另一个地址空间时进行地址翻译。每一个非透明桥(NTB)端口都有两套基地址寄存器(BAR),一套是给主设备端用的,另一套是给从设备端用的。基地址寄存器可用来定义在非透明桥另一端的内存地址空间的地址翻译窗口,并允许这个翻译被映射到本地的内存或I/O空间。

非透明桥允许桥两边的主机通过便笺寄存器、门铃寄存器和心跳消息来交换一些状态信息。便笺寄存器在非透明桥的两端都是可读写的,但是,便笺寄存器的数量在具体的实现中是可以不同的。他们可以被桥两边的设备用来传送一些状态信息,也可作为通用的可读可写寄存器使用。 门铃寄存器被用来从非透明桥的一边向另一边发送中断。非透明桥的两边一般都有软件可以控制的中断请求寄存器和相应的中断屏蔽寄存器。这些寄存器在非透明桥的两边都是可以被访问的。心跳消息一般来自主设备端往从设备端的主机,可用来指示它还活着。从设备主机可监控主设备主机的状态,如果发现出错,它就可以采取一些必要的措施。通过门铃寄存器可以传送心跳消息。当从设备主机没有收到一定数量预先规定好的心跳消息时,就可以认为主设备的主机出错了[1]。

2 视频处理系统架构

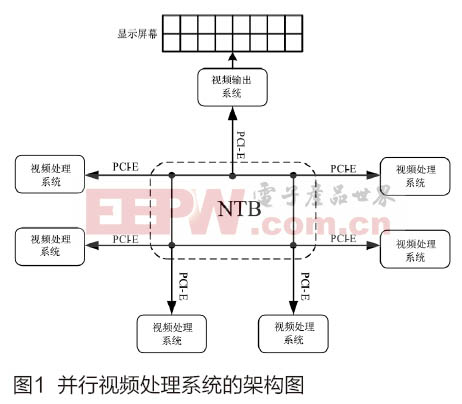

本文提出了一种并行视频处理的系统架构,具体见图1,该并行视频处理系统包括了多个视频处理系统,一个非透明桥和一个视频输出系统。视频处理系统主要完成规定的各种视频处理,视频输出系统负责完成视频数据对屏幕的输出。非透明桥(NTB)用于连接视频处理系统和视频输出系统,控制数据和视频数据的交互通过非透明桥芯片实现;非透明桥为系统之间提供一个高速的数据交换通道和通信的桥梁。多个视频处理系统和一个视频输出系统通过PCI-E总线和非透明桥(NTB)相连接,利用NTB的交换(switch)功能,实现多个视频系统之间的点对点通信。各个视频处理系统之间相互连接,每个视频处理系统都可以单独和任意一个视频处理系统之间通信和进行海量数据传输;视频输出系统通过非透明桥的连接,也可以和任意一个视频处理系统连接,视频处理系统可以将任意一个视频处理系统的数据输出给屏幕显示。每个视频处理系统具有一个或多个外围设备相关联的信息处理模块,外围设备信息通过PCI-E协议进出传输。

数据传输中采用了高速的PCI-E传输通道,该并行架构系统解决了海量视频数据传输的瓶颈问题,为并行处理提供了硬件基础。单通道的PCI-E总线[2]带宽可以达到10Gbps,该总线有X1、X2、X4、X8和X16、X32(X32目前还不支持)通道规格可选,如果采用X4,通道的总带宽可以达到40Gbps(PCI-E 2.0协议),单方向带宽可以达到20Gbps。超宽的PCI-E数据传输通道为海量视频数据提供了高速通道。例如逐行扫描制式,帧率通常为60Hz的 1080P无压缩视频,传输需要3Gbps的数据通道,采用PCI-E通道可以传输多个1080P视频数据,保证了视频信号传输的流畅。

非透明桥 PCI-E协议 并行运算 视频 同步机制 201508 相关文章:

- 基于PCIe总线的多路复用DMA高速传输系统的设计(09-12)

- 一种具有主从自适应功能的CPCI通用处理模块设计(01-18)

- 在FPGA上实现H.264/AVC 视频编码标准(07-23)

- 用FPGA替代DSP实现实时视频处理(08-26)

- DSP+FPGA嵌入式多路视频监控系统硬件平台(04-10)

- 基于DSP的视频采集驱动程序的实现(07-21)