让XDC时序与约束为您效力

您还可使用数控阻抗正确做IO端接并增加系统的 SI,无需使用外部端接方案。如果没有信号驱动 I/O,例如将 I/O 连接到外部连接器,这时您还必须考虑 I/O 的影响。这种情况下,您可使用 I/O 约束实现上拉或下拉电阻,以防止由于 FPGA 输入信号悬置而导致系统问题。

当然,您也可以使用物理约束在 I/O block 内放置最终的输出触发器,以改善设计的时序。这样做能缩短clock to out的时间。您也可以对输入信号做相同的处理,以使设计满足引脚到引脚的建立和保持时间要求。

物理约束从布局开始

您可能出于多种原因想对布局进行约束,例如帮助达到时序要求,或者在设计的不同区域间实现隔离。就此而言,有三种类型的约束很重要:

• BEL –将网表单元放在 slice 中的基本的逻辑元素。

• LOC –将网表的单元放在器件内的一个位置。

• PBlock – 可使用物理(或“P”)block 将逻辑 block 约束到 FPGA 的一个区域。

因此,LOC 允许在器件内定义一个 slice 或其它位置;BEL 约束可用来定义触发器在 slice 中使用的更精细粒度。当对设计的大面积区域进行分段时,PBlock 可用来将逻辑集合在一起。PBlock 的另一个用途是在执行部分重配置时定义逻辑区域。

有些情况下,您需要将较小的逻辑功能放在一组,以确保时序达到最佳。尽管可以用 PBlock 来实现,但更常见的方法是使用相对放置的宏命令。

相对放置的宏命令(RPM)允许将 DSP、触发器、LUT 和 RAM 等设计元素在布局中放在一起。

与 PBlock 不同,RPM 不会将这些元素的位置约束在器件的特定区域(除非您想这样做),而是在布局时将这些元素放在一起。将设计元素放在一起能实现两个目标。这样能改善资源效率,让您能够精细调节互联长度,以实现更好的时序性能。

要将设计元素放在一起,可使用三种类型的约束,这些约束用 HDL 源文件进行定义。

• U_SET 可定义一个与层级无关的单元 RPM 集。

• HU_SET 可定义有层级的单元 RPM 集

• RLOC给定义好的SET分配相对位置。

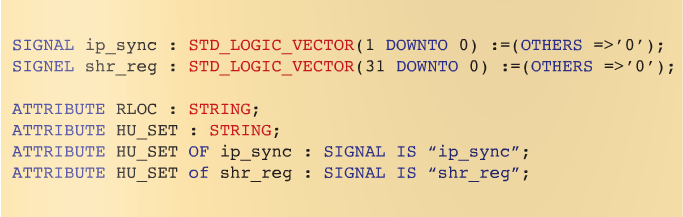

RLOC 约束被定义为 RLOC = XmYm,其中 X 和 Y 与 FPGA 阵列的坐标有关。当定义 RLOC 时,既可以用相对坐标也可以用绝对坐标,取决于您是否添加了 RPM_GRID 属性。添加这个属性后,该定义将成为绝对坐标而非相对的。由于这些约束在 HDL 中定义,如图 4 所示,因此在将约束添加到 HDL 文件之前,通常需要首先运行布局布线设计反复,以便正确定义布局。

图 4 – 源代码中的约束

总之,理解时序和布局约束并学习如何正确使用它们,对于在赛灵思可编程逻辑设计中获得最佳结果质量至关重要。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)