让XDC时序与约束为您效力

作者:Adam Taylor e2v 公司首席工程师 aptaylor@theiet.org

时序和布局约束是实现设计要求的关键因素。本文是介绍其使用方法的入门读物。

完成 RTL 设计只是 FPGA 设计量产准备工作中的一部分。接下来的挑战是确保设计满足芯片内的时序和性能要求。为此,您经常需要定义时序和布局约束。我们了解一下在基于赛灵思 FPGA 和 SoC 设计系统时如何创建和使用这两种约束。

时序约束

最基本的时序约束定义了系统时钟的工作频率。然而,更高级的约束能建立时钟路径之间的关系。工程师利用这类约束确定是否有必要对路径进行分析,或者在时钟路径之间不存在有效的时序关系时忽视路径。

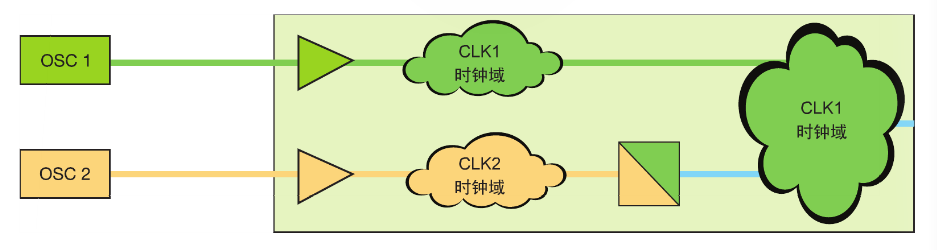

默认情况下,赛灵思的 Vivado® 设计套件会分析所有关系。然而,并非设计中的所有时钟之间都有可以准确分析的时序关系。例如当时钟是异步的,就无法准确确定它们的相位,如图 1 所示。

图 1–时钟域 CLK1 和 CLK2 相互之间异步。

您可通过在约束文件中声明时钟组来管理时钟路径之间的关系。当声明时钟组时,Vivado 工具不会对组内定义的时钟之间的任何方向执行时序分析。

为了有助于生成时序约束,Vivado 工具将时钟定义为三种类型:同步、异步或不可扩展。

• 同步时钟具有可预测的时序/相位关系。通常主时钟及其衍生时钟符合这种特性,因为它们具有公共的根起源和周期。

• 异步时钟之间不具备可预测的时序/相位关系。通常不同的主时钟(及其衍生时钟)符合这种特性。异步时钟有不同的起源。

• 如果超过1,000个周期后,仍无法确定公共周期,那么两个时钟就是不可扩展的。如果是这种情况,将使用 1,000 个周期内的最差建立时间关系。不过,无法保证这就是实际的最差情况。

使用 Vivado 生成的时钟报告来确定您所处理的时钟是哪种类型。该报告可帮助您识别异步和不可扩展时钟。

声明多周期路径能实现更合适而且要求放松的时序分析,从而让时序引擎集中处理其它更关键的路径。

识别出这些时钟后,您就可利用“set clock group”约束禁止它们之间的时序分析。Vivado 套件使用的是赛灵思设计约束 (XDC),其基于广泛使用的 Tcl 约束格式的 Synopsys 设计约束 (SDC)。通过 XDC 约束,您可使用以下命令定义时钟组:

set_clock_groups -name -logically_exclusive -physically_exclusive -asynchronous -group

-name 是为组赋予的名称。-group 选项是定义组成员(即没有时序关系的时钟)的位置。当有多个用来驱动时钟树的时钟源可供选择,包括 BUFGMUX 和 BUFGCTL,应使用 logically 和 physically exclusive 选项。从而,这些时钟不能同时出现在时钟树上。所以,我们不希望 Vivado 分析这些时钟之间的关系,因为它们是互斥的。最后,–asynchronous 约束可用来定义异步时钟路径。

建立时序关系的最后一个方面是考虑时钟的非理想关系,尤其是抖动。您需要考虑两种形式的抖动:输入抖动和系统抖动。输入抖动出现在主时钟输入上,体现了实际跳变出现时间与理想条件下跳变出现时间之间的差异。系统抖动源自设计中存在的噪声。

您可以使用 set_input_jitter 约束来定义每个主输入时钟的抖动。同时,使用 set_system_jitter 约束为整个设计(所有时钟)设定系统抖动。

时序例外

当有时序例外时,您还必须关注已定义的时钟组内发生了什么。然而,什么是时序例外呢?

一种常见的时序例外是只有每隔一个时钟周期所采样的结果。另一种情况是将数据从慢时钟传输到更快的时钟(或相反),其中两个时钟都是同步的。事实上,这两种时序例外一般被称为多周期路径,如图 2 所示。

图 2–多周期路径是一种时序例外的例子。

为这些路径声明多周期路径能实现更合适而且要求放松的时序分析,从而让时序引擎集中处理其它更关键的路径。最后的益处是能够提高结果质量。

您可以在 XDC 文件中使用以下 XDC 命令声明多周期路径:

set_multicycle_path path_ multiplier [-setup|-hold]

[-start|-end][-from ] [-to ]

[-through

]

当您声明多周期

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)