让XDC时序与约束为您效力

路径时,实际上是将建立或保持(或二者皆有)分析要求与 path_mutiplier 相乘。例如在上面的第一个实例中,每两个时钟周期有一次输出,因此对于建立时序而言 path_multiplier 是 2。由于多周期路径既可应用到建立时间又可应用到保持时间,那么您可以选择其应用位置。当您声明建立时间乘数时,最佳做法通常是使用下面的公式同时声明一个保持时间乘数。

保持周期 = 建立乘数 – 1 – 保持乘数

这对于我们所介绍的下列简单实例意味着,保持乘数由下面这个公式确定:

保持乘数 = 建立乘数 – 1,当使用公共时钟时。

为了演示

多周期路径的重要性,我创建了一个简单实例,您可在这里下载。在 XDC 文件中有一个实例包含了建立和保持这两个已被同时声明的多周期路径。

物理约束

最常用的物理约束是 I/O 引脚布局和与 I/O 引脚有关的参数定义,例如标准驱动强度。不过,还有其它类型的物理约束,包括布局、布线、I/O 和配置约束等。布局约束能够定义单元的位置,而布线约束可用来定义信号的布线。I/O 约束可用来定义 I/O 位置及其参数。最后,配置约束可用来定义配置方法。

同样,也有一些约束不属于这几组约束。Vivado 设计套件包含三种这样的约束,它们主要用于网表中。

• DONT_TOUCH – 该约束可用来阻止优化,这样当实现安全关键型或高可靠性系统时该约束会非常有用。

• MARK_DEBUG – 该约束可用来保存 RTL信号,以便随后用于调试。

• CLOCK_DEDICATED_ROUTE – 该约束可用来识别时钟布线。

最常用的约束与 I/O 布局和 I/O 的配置有关。将 I/O 放在 FPGA 上,需要使用布局约束找到物理引脚,使用 I/O 约束配置 I/O 标准和斜率等 I/O 属性。

现代化的 FPGA 支持多种单端和差分 I/O 标准。这些均可通过 I/O 约束来进行定义。不过,您必须确保遵守 I/O Banking 规则,这取决于最后的引脚布局。

但什么是 I/O Banking 规则?将 FPGA 中的用户 I/O 分组为若干个 Bank,每个 Bank 包含多组 I/O。这些 Bank 具有独立的电压源,能支持多种 I/O 标准。在 Zynq®-7000 All Programmable SoC(以及其它 7 系列器件)中,I/O Bank 被进一步分为高性能和大范围这两个大的组别。这种类别划分能进一步约束性能,并要求工程师针对接口使用正确的类别。

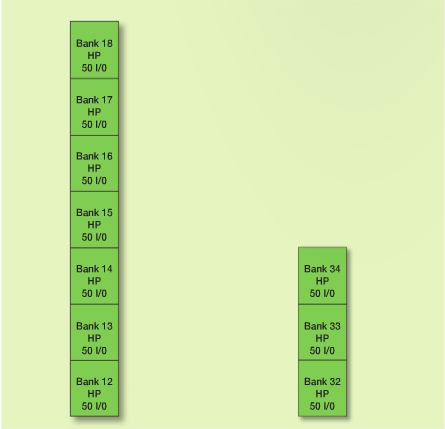

高性能 (HP) 类别针对更高的数据速率进行了精心优化。它使用更低的工作电压,而且不支持 LVCMOS 3v3 和 2v5。另一个是大范围 (HR) 类别,其可处理 HP 不支持的更多 I/O 标准。因此,HR 支持传统的 3v3 和 2v5 接口。图 3 给出了这些 Bank。

图 3 – 赛灵思 7 系列器件上的高性能(左)和大范围 I/O Bank

当您决定为信号使用哪种 Bank 后,仍然可以更改信号驱动强度和斜率。这些都是硬件设计团队很感兴趣的指标,因为他们要努力确保单板的信号完整性达到最优。选择结果还会影响单板设计的时序。为此,您可以使用信号完整性工具。

SI 工具需要 IBIS 模型。当您打开了Impelmented Design时,您可使用 File->Export->Export IBIS 模型选项从 Vivado 工具中提取设计的 IBIS 模型。然后,使用该文件关闭解决系统级 SI 问题和最终 PCB 布局的时序分析。

如果设计团队整体上对 SI 性能以及系统的时序感到满意,您就会得到针对设计中 I/O 的多个约束,如下所示。

set_property PACKAGE_PIN G17 [get_ports {dout}] set_property IOSTAN- DARD LVCMOS33 [get_ports

{dout}]

set_property SLEW SLOW [get_ports {dout}]

set_property DRIVE 4 [get_ ports {dout}]

对于 HP I/O Bank,

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)