ARM手记之芯唐M0系列

1.ARM Cortex-M0 内核

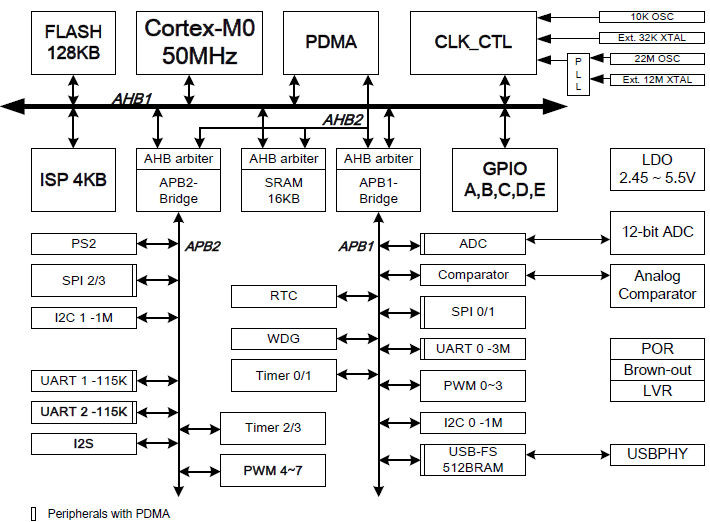

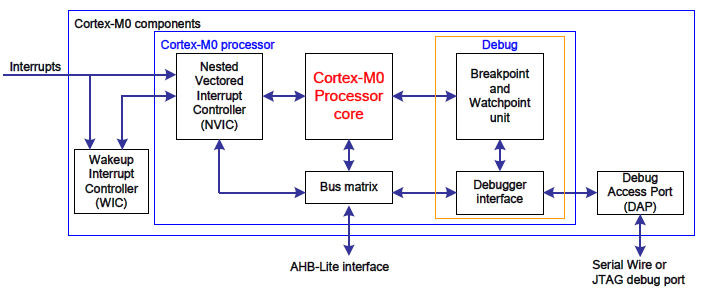

Cortex-M0处理器是32位多级可配置的RISC处理器。它有AMBA AHB-Lite接口和嵌套向量中断控制器(NVIC),具有可选的硬件调试功能,可以执行Thumb指令,并与其它Cortex-M系列兼容。支持两种模式:Thread模式和Handler模式;异常时,系统进入Handler模式,复位时,系统进入Thread模式。

1)基本特性:

特征:系统支持小端(little-endian)数据访问,提供单指令32-bit 硬件乘法器。

NVIC:提供32个外部中断,具有4级中断优先级。有专用的不可屏蔽中断NMI。支持电平和脉冲中断触发。中断唤醒控制器WIC,支持极低功耗休眠模式。

调试:提供4个硬件断点,2个观察点,用于非侵入式代码分析的程序计数采样寄存器,单步向量捕获能力。

总线接口:提供简单的集成到所有系统外设和存储器的单一32位AMBA-3 ABH-Lite系统接口;支持DAP(Debug Access Port)的单一32位的从端口。

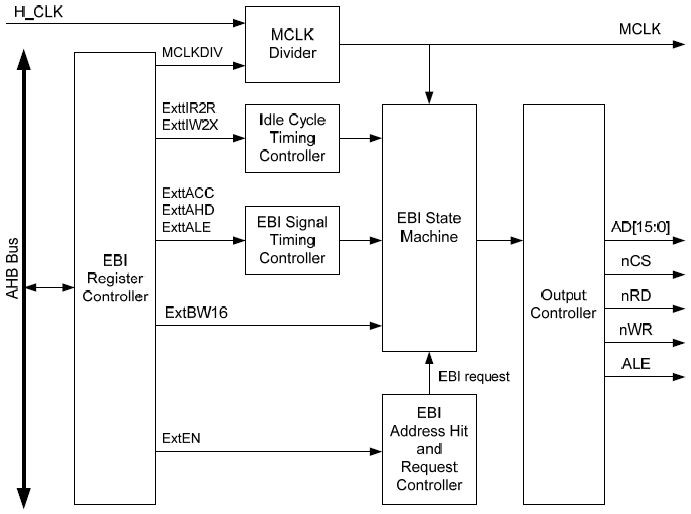

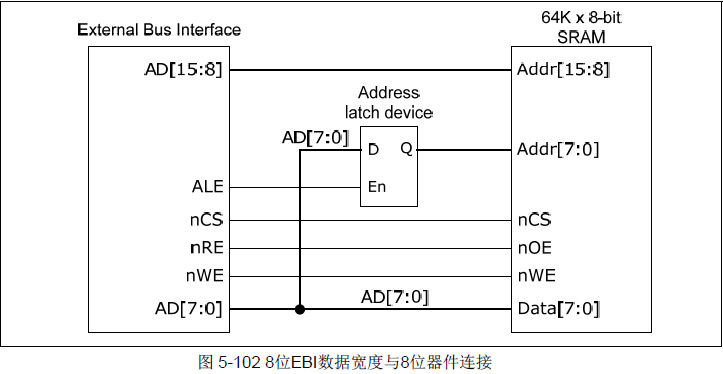

2)外部总线接口EBI

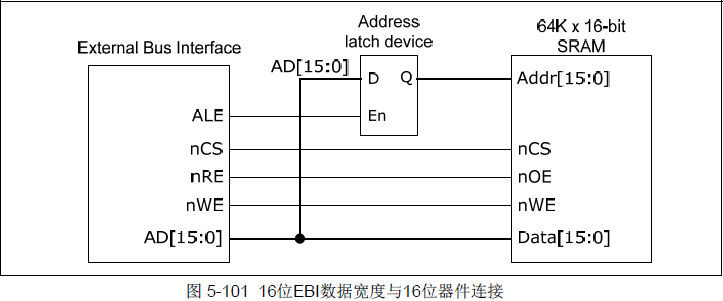

为节省外部设备与芯片的连接线,EBI支持地址总线与设备总线多路复用,且地址锁存使能信号ALE支持地址和数据周期的差别。

支持最大外部设备64KB(8位数据宽度)/128KB(16位数据宽度),支持可变的数据访问时间(tACC)、地址锁存使能时间(tALE)和地址保持时间(tAHD)。

EBI地址在0x6000 0000至0x6001 FFFF,总共内存空间为128KB,当系统申请的地址在EBI的内存空间,相应的EBI片选信号有效,EBI状态机工作。

2.系统管理器

1)系统复位

复位源包括:上电复位、复位脚(/RESET)上有低电平、看门狗复位、低压复位、欠压检测复位、Coretex-M0 单片机复位、系统复位。

系统复位和上电复位使整个芯片复位,包括外设。

2)系统电源

该器件的电源分为3类:a.由AVDD和AVSS提供的模拟电源,为模拟部分工作提供电压;b.由VDD和VSS提供的固定的2.5V的数字电源,用于数字操作和I/O引脚的内部稳压电源;c.VBUS提供给USB的电源,用于USB模块传输操作。

内部电压调节器输出LDO和VDD33,需要在相应的引脚上外接电容。

3)系统内存映射

NUC1xx 提供4G字节的寻址空间,NUC1xx系列仅支持小端数据格式,ROM、SRAM和控制寄存器统一编址。

4)系统定时器

Cortex-M0 包含一个24位系统定时器SysTick,使能后,定时器从SysTick 当前寄存器(SYST_CVR)的值向下计数到0,下一个时钟边缘,重新加载寄存器(SYST_RVR) 的值。当计数器减到0时,标志位COUNTFLAG置位,在读数时,清COUNTFLAG标志位。

5)嵌套向量中断控制器 (NVIC)

Cortex-M0 提供中断控制器,用于总体管理异常,NVIC和处理器内核紧密相连。

NVIC结构支持32(IRQ[31:0])4级离散中断优先级,当接受任何中断时,ISR的开始地址可从内存的向量表中取得,当开始地址取得时,NVIC将自动保存处理状态到栈中,包括以下寄存器“PC, PSR, LR, R0~R3, R12” 的值. 在ISR结束时, NVIC 将从栈中恢复相关寄存器的值,进行正常操作,因此花费少量时处理中断请求。向量表的基地址为0x00000000. 向量表包括复位后栈的初始值,所有异常处理器的入口地址. 向量号表示处理异常的先后次序。

6)系统控制寄存器

系统控制寄存器控制了Cortex?-M0的状态和操作模式,包括CPUID、Cortex?-M0中断优先级和Cortex?-M0电源管理。

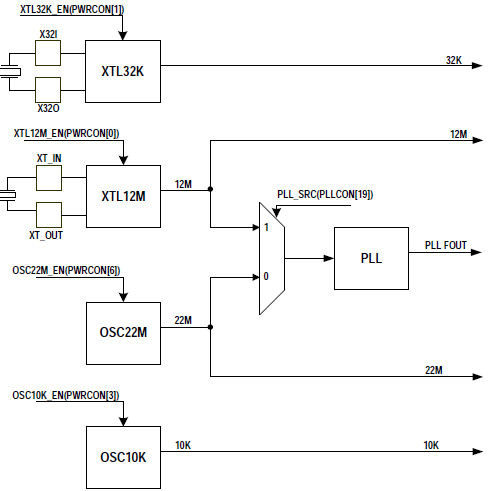

3.时钟控制器

时钟控制器为芯片提供时钟源. 包括AMBA接口模块和所有外围设备时钟,时钟发生器由如下5个时钟源组成:一个外部 32KHz 晶振、一个外部 12MHz 晶振、一个可编程的 PLL FOUT(PLL 由 12M 和 22M组成)、一个内部 22MHz RC 振荡器、一个内部 10KHz 振荡器。

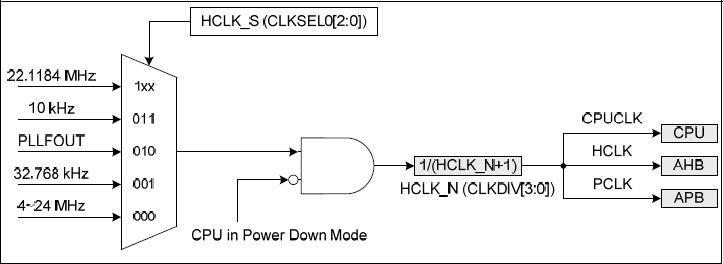

时钟源切换取决于寄存器HCLK_S(CLKSEL0[2:0]):

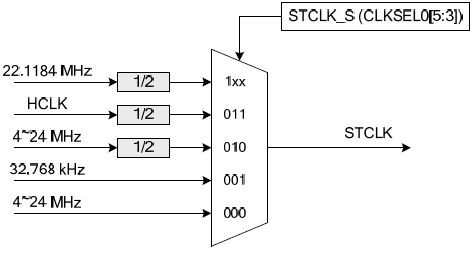

Cortex?-M0内核的SysTick时钟源可以选择CPU时钟或外部时钟(SYST_CSR[2]),如果使用外部时钟,SysTick时钟(STCLK)有5个时钟源,

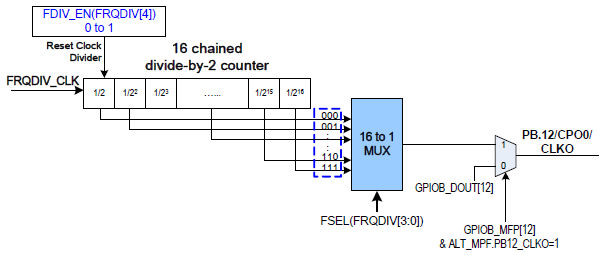

该器件包含分频器,由16级2分频移位寄存器组成. 因此有16种分频选择从 Fin/21 到 Fin/216 ,其中 Fin 为输入到时钟分频器的时钟频率.

4.存储器

1)程序存储器

具有32K/64K/128K字节的片上FLASH ROM,用于存储程序代码(APROM),4kB在系统编程(ISP)加载程序内存(LDROM),用于存储ISP引导代码,用户可以通过ISP/IAP更新FLASH中的程序,用户设置Config0以选择从AP_ROM或LD_ROM开始。对于64/32K字节的

ARM芯唐M0系 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)