基于FPGA的动态局部可重构实现方法

时间:06-04

来源:互联网

点击:

到处理器系统中。

3.2.2 综合实现所有外设模块

借助Xilinx ISE工具综合实现所有外设模块,应该注意的是在综合过程中,只有顶层模块的I/O缓冲在综合时打开,其它子模块的I/O缓冲在综合时是不能打开的。

3.2.3 利用PlanAhead手工修改布局布线和装配PR设计

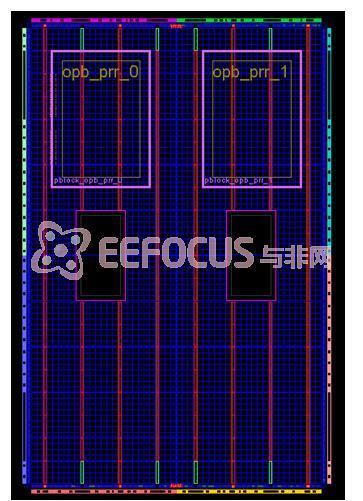

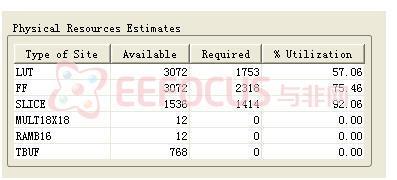

可重构模块硬件资源分配以及硬件资源分配评估、添加时序和管脚的约束都应该在这一步成功完成。利用PlanAhead工具和ISE集成的FPGA editor工具能够准确观察到整个FPGA底层的布局布线图,同时借助PlanAhead工具直观看到可重构模块和静态模块的布局布线图以及它们的资源占用情况[4]。图5所示的是系统的布局布线图,图6所示的是资源分配的情况。

图5 系统的布局布线图

图6 PRR Left重构模块的资源占用统计

在总线宏busmacros、全局时钟逻辑等手工放置好之后,将进入装配阶段,将所有静态逻辑和局部重构逻辑整合到位流文件中。在生成FPGA的初始化位流文件和局部重配置文件之后,利用EDK的Launch EDK Shell工具来生成加载FPGA时需要的System ACE文件。下一步就可以上板调试了。

动态局部可重构 OPB总线 FPGA PlanAhead EDK 相关文章:

- 比较OPB总线和FSL总线(12-15)

- OPB总线学习日志(12-14)

- OPB总线仲裁器的RTL设计与FPGA实现(11-19)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)