OPB总线仲裁器的RTL设计与FPGA实现

0 引言

随着 SOC 设计技术的发展,为了使IP 核集成更快速、更方便,缩短进入市场的时间, 迫切需要一种标准的互联方案。CoreCONnect 正是在这一背景下为SOC 设计的总线架构。按 照数据访问速度它可分为三层总线,分别是处理器内部总线PLB(Processor Local Bus)、片上 外围总线OPB(On-ChipPeripheral Bus)和设备控制总线DCR(Device Control RegiSTer)。 OPB 总线是为UART、GPIO 等慢数据率设备提供接口的总线。由于集成到总线中的功能模 块越来越多,对于共享总线系统,片上仲裁是使得各个模块有效运作的必要手段。目前关于 OPB 总线仲裁器这方面的研究报道较少,为了探寻在不同的系统负载和系统应用下选择最 佳的OPB 总线仲裁方案,本文基于固定优先级和LRU 两种算法,利用自顶向下的设计方法, 设计了OPB 总线的仲裁器,并对其综合结果做了比较。

1 OPB 总线仲裁机制

OPB 总线支持32 位数据/地址位宽,读和写数据总线分开,支持重试模式,支持突发 (burst)传输模式,支持DMA,检测总线超时功能,支持多个主设备的仲裁。OPB 总线的 系统结构分为三个部分:主设备(Master),从设备(Slave)和总线逻辑。信号命名有三种: Mn_打头的,是master 的输出;Sln_打头的,是Slave 的输出;OPB_打头的,是总线逻辑 的输入或输出。OPB 总线允许有多个master,当这几个master 同时发出请求要求使用总线时, 就必须对他们的请求进行仲裁,并确定他们使用总线的优先级,这就是仲裁器的作用。OPB 总线仲裁器的输入输出信号如图1 所示。

SYSCLK 和RESET 为OPB 总线的系统时钟和复位信号。Mn_REQUEST 为4 个master 的请求信号,OPB_MnGRANT 为仲裁器发出的授权信号,OPB_select 是master 收到授 权信号后发出的占用总线信号,OPB_ABUS 为地址总线,OPB_DBUS 为数据总线, OPB_XFERACK 为slave 数据传输完的响应,OPB_RNW 是读写使能信号,OPB_BUSLOCK 是master 锁定对总线使用权的信号,ARB_DBUS 和ARB_DBUSEN 是仲裁器的数据总线和 使能信号,ARB_XFERACK 是仲裁器传输数据完成的响应信号。OPB_TOUTSUP 是slave 超时禁止的信号,OPB_TIMEOUT 是总线超时信号。

仲裁过程说明如下:

Master 首先发出Mn_REQUEST 信号申请占用总线,仲裁器根据总线占用情况和优先权 算法发出OPB_MnGRANT 信号,得到最高优先权的master 拉高Mn_SELECT 信号,其他 master 把这个信号置低,这4 个select 信号通过或逻辑形成OPB_SELECT 信号输入给仲裁 器。

同时发送地址 Mn_ABUS,也是通过或逻辑转变成OPB_ABUS 输入给仲裁器。OPB 总 线有多个slave 设备,每个slave 都有自己的地址空间值,Master 发送的Mn_ABUS 正是包 含了他所要使用的slave 的地址值,slave 会对值进行比较,如果相等,master 就可以对slave 进行读写操作。

读操作时,master 拉高OPB_RNW,仲裁器拉高ARB_DBUSEN,并通过ARB_DBUS 输 出数据。写操作时,master 拉低OPB_RNW,通过OPB_DBUS 输入数据。当有效数据传输完 成后,仲裁器会拉高ARB_XFERACK 信号响应。Master 在收到响应后,会拉低Mn_SELECT 信号,结束此次总线事务。

2 OPB 总线仲裁器的设计

采用自顶向下的设计方法,将设计分成4 个模块,分别为优先级逻辑模块,仲裁模 块,看门狗超时模块和锁定/停靠模块。原理图如图2 所示。

图2 仲裁器设计原理图

1) 优先级逻辑模块

这个模块采用两种不同的算法进行设计,分别是LRU(Least Recently Used)算法和固定 优先级算法[1]。

a) LRU 算法

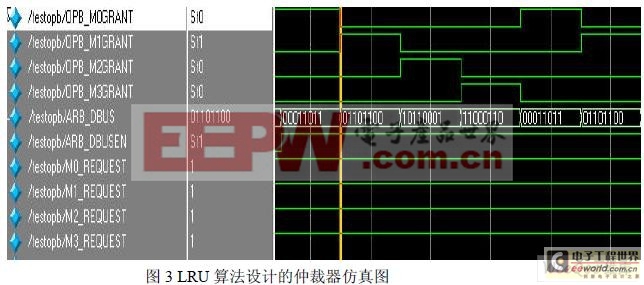

LRU 算法就是根据master 的编号循环得到优先级,保证每个设备都有机会获得总线。我 们设计的是最多支持4 个master 的仲裁器,所以采用一个8 位的寄存器,用来存放4 个master 的二进制编号。每个周期都要更新这个寄存器值,将得到最高优先级的master 编号放到最 低优先级,其他3 个master 编号各进一级。用这种算法设计的仲裁器的仿真结果如图3。

其中 ARB_DBUS 读出来的数据正是寄存器中保存的master 编号,优先级从高位到低位 递减。00,01,10,11 代表master 的编号0,1,2,3。当4 个master 同时发出请求时,第 一个时钟周期将优先级授权给master0,第二个时钟周期时,master0 的优先级降为最低,其 他三个优先级递进,所以此时授权给master1。后面的周期依次循环,4 个master 将轮流获 得授权。

b) 固定优先级算法

固定优先级算法将 4 个master 的优先级按顺序固定下来,不会改变[2]。这种算法设计更 简单,不需要每周期对master 的优先级更新。设计时优先级寄存器中的值只在总线执行写 操作

- 基于FPGA的动态局部可重构实现方法(06-04)

- 比较OPB总线和FSL总线(12-15)

- OPB总线学习日志(12-14)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)