OPB总线仲裁器的RTL设计与FPGA实现

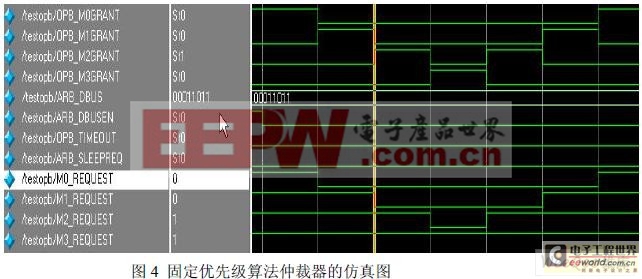

和复位时才会改变,平时固定不变。仿真结果见图4。

ARB_DBUS 是写入的4 个master 的优先级顺序,master0 为最高,master3 最低。当4 个master 同时发出请求时,授权给master0;当master0 不发出请求,其他三个master 发出 请求时,则根据优先级顺序,授权给master1;依此类推。

2)仲裁逻辑模块

从优先级逻辑模块得到的优先级寄存器信号,将被输入到仲裁逻辑模块。用以对4 个 master 的Mn_REQUEST 请求信号排序,然后优先级从高到低排序的master 中,第一个拉高 请求信号的master 将被授权占用总线。仲裁逻辑模块输出的授权信号是最原始的,这个信 号还要经过锁定/停靠逻辑模块处理才能得到最终的授权信号(OPB_MnGRANT)。

3) 看门狗超时逻辑模块

看门狗逻辑用来监控OPB 的控制信号,当master 在16 个时钟中期内没有能够收到slave的响应信号( OPB_XFERACK ) 和超时禁止信号( OPB_TOUTSUP ), 将会拉高 OPB_TIMEOUT 超时信号[3]。这部分的设计采用一个4 位计数器对时钟进行记数。

4) 锁定/停靠逻辑模块

优先级锁定是得到最高优先级的master 同时拉高OPB_BUSLOCK 信号,这样在这个信 号被置低之前,这个master 将始终得到总线的占用权,仲裁逻辑将不启用。此时不管master 是否发送请求,都不会对仲裁产生影响。优先级的锁定是通过将仲裁逻辑得到的原始优先级 信号和OPB_BUSLOCK 信号相与后产生的。优先级停靠是当没有新的master 发出请求信号 时,总线继续授权给当前占用总线的master。这里设计了一个四位寄存器用来追踪最近占用 总线的master 编号。

最后,通过altera 公司的CycloneII FPGA 对两种设计进行综合[4],并对综合结果进行比 较。并采用cadence 公司的conformal 进行RTL 代码和网表之间的形式验证。表1 为综合 和形式验证结果。

得出的结论是:固定优先级算法设计简单,占用资源少,可以达到较高的应用频率。但 这种算法使优先级高的设备占着总线不放,当总线事务繁忙时,优先级低的设备将申请不到 总线,所以只适用于总线使用率低,负载低的应用。而LRU 算法虽然更占资源,频率也低 点,但这种算法授权更加公平,使所有设备都有机会申请到总线,适用于总线使用率高,负 载高的应用。

3 结束语

本文通过对 OPB 总线仲裁器两种算法的研究,比较了两种算法的性能优劣并得出结论, 固定优先级算法设计简单,占用资源少,可以达到较高的应用频率,能够保证主要处理器的 运行速度,但缺乏公平性;LRU 算法更占资源,频率较低,但具有公平性,适用于总线使 用率高,负载高的应用。对不同的总线负载和使用率情况下选择最佳的OPB 总线仲裁方案 提供了依据,对高效的系统设计和嵌入式应用有重要的参考价值和指导意义。

- 基于FPGA的动态局部可重构实现方法(06-04)

- 比较OPB总线和FSL总线(12-15)

- OPB总线学习日志(12-14)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)