利用FPGA和多通道光模块组合长距离传送高速数据

目前基于铜电缆的高速串口能够以数千兆位速率进行数据传送,并可通过使用多个并行通道达成超过100Gbps的数据传输率,不过传送的距离却受到限制,一个可以改善传输距离的作法是使用光互连来取代铜电缆,Altera和Avago公司共同发展出结合FPGA以及光发射和接收模块的单一集成方案,可以取代铜电缆互连和多个卡边缘光收发器。

介绍

数据中心以及互联网上越来越大量的数据移动对于尝试赶上的基础设施形成压力,核心功能如存储次系统、数据交换机和路由器,甚至是计算系统都受到输入输出的限制,外部数据的移动则受限于数据可以在连接所有交换机、路由器和存储阵列的电缆或其他互连机制上以多快的速度和多远的距离移动。

目前基于铜电缆的高速串口能够以数千兆位速率进行数据传送,并可通过使用多个并行通道达成超过100Gbps的数据传输率,但要达到如此速度需付出一个代价,那就是受到限制的传输距离,基本上,数据率越高所能传送的距离就越短,除非在信号完整性、功率以及通道材料成本上做出牺牲。

为了补偿信号的劣化,通常使用复杂的信号处理功能在发射端和接收端进行信号均衡,这样的方式搭配上经过仔细设计但价格昂贵的铜电缆可以提供数米长度的距离延伸,足够让单一机架间的设备互连,不过如果要让数据在数据中心或网络中心的机架间传送,就需要更长的电缆,在许多情况下,面临的成本和大量电缆问题使这种作法变得不切实际。

光互连

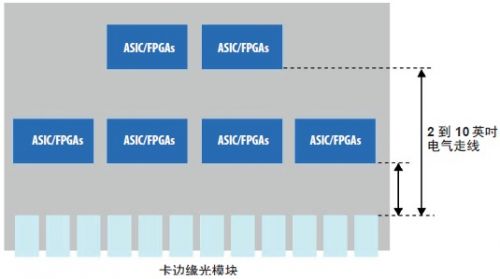

一个可以改善传输距离的方法是使用光学方式来取代铜电缆,光纤连接目前虽然已经进入数据通信产业,但许多连线需要非常耗电的卡边缘光接口模块,并仍然面临系统逻辑到光模块的电气互连问题,请参考图1。高速串口的逻辑部分通常会在FPGA中实施,原因是这类器件可以提供设计工程师在电路板特性、功能以及输入输出选择的高灵活度,不过这样做FPGA的引脚必须连接光模块,无可避免地带来电路板上的高速走线。

|

| 图1:网络交换机或路由器的典型电路板布局显示输入输出逻辑和光模块间的距离 |

FPGA的好处

FPGA的灵活度和可重配置能力使它们成为需要各种高速输入输出系统的理想方案,达到1Gbps传送能力的高速LVDS串口和串化/解串器(SERDES)首先被集成到了FPGA中,接着是超过3Gbps的更高速度SERDES,目前FPGA已经集成10Gbps甚至更高数据率的SERDES,举例来说,Altera公司的新28nm Stratix V FPGA 就可以达到28Gbps的速度。除了高速输入输出能力外,FPGA还提供有数百万个可配置逻辑门、大量的片上静态存储器以及其他专门的系统资源,包括处理器核心、锁相环(PLL)、数字信号处理(DSP)方块、PCI Express® (PCIe®)通道以及存储控制器等。

所有FPGA上的资源允许设计工程师将许多系统功能配置到器件的逻辑电路上,缩减系统电路板上所需的电路数量,另外,FPGA的可配置特性使得设计工程师可以更改逻辑来增加或移除功能、修补逻辑臭虫或者改善性能。

|

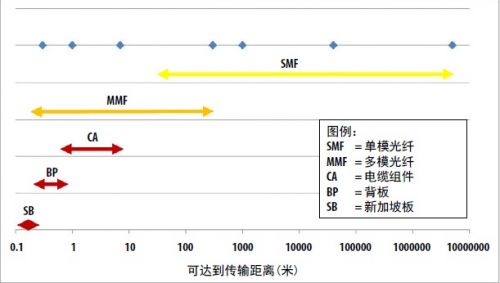

| 图2:对于10Gbps的数据传送,数据可以移动的最大距离有着大幅度差异,主要依使用的为铜电缆(红色部分)或光接口(橘色和橙色)而定 |

虽然在10Gbps数据率下FPGA到光模块的距离仅数英吋,但就算电路板上数英吋的走线路径都可能损害信号的品质,图2显示了10Gbps数据流可以传送的距离会因使用的接口而有所不同,因此为了确保光模块可以得到最佳的信号,如何将FPGA连接到光连接端口发射器输入和接收器输出的距离极小化就成了必须面对的挑战。

集成型光封装

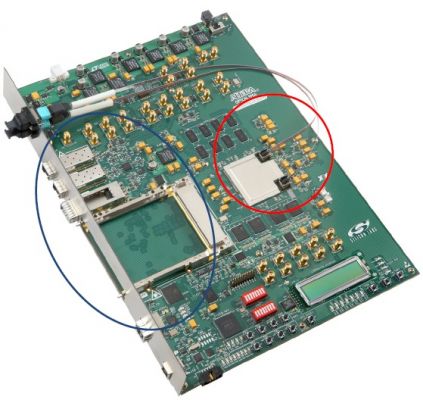

为了把FPGA和光模块间的距离极小化并降低整个芯片到模块连结的功率和使用材料,Altera和Avago公司共同开发了结合FPGA以及光发射和接收器模块到单一集成封装,可以取代多个外部卡边缘光收发器的产品,如图3中展示电路板上的蓝圈部分。光学FPGA技术展示使用了Altera公司的Stratix IV GT FPGA,提供32个高速SERDES连接端口,每个端口可以达到11Gbps的数据传输率,并有12个连接端口直接和Avago公司的MicroPOD™光模块连接。

12个光通道的每一个都可以独立运行或作为高容量通道的一部分,以方便通过高成本效益方式提供目标带宽,并行光学相似于使用并行通道电气接口,例如PCI Express的多重通道达到目标带宽的电子信号作法。

|

| 图3:评估电路板上包含有Altera公司的FPGA以及Avago公司的MicroPOD 12通道光发射器和接收器(红圈部分),电路板上还有传统的卡边缘光收发器模块(蓝圈部分)提供设计工程师进行性能比较 |