基于FPGA的UART扩展总线设备逻辑设计

1 引言

在嵌入式领域,由于UART 具有操作简单、工作可靠、抗干扰强、传输距离远(组成 485 网络可以传输1,200 米以上),设计人员普遍认为UART 是从CPU 或微控制器向系统的 其他部分传输数据的最佳方式,因此它们被大量地应用在工业、通信和家电控制等嵌入式领 域。而通常处理器都会自带一个UART 串口,实际应用中一个串口往往不够用,需要进行 UART 串口扩展。而本文在分析了片内总线技术和UART 的工作原理的基础上了实现UART 总线设备的设计,使主控芯片可以控制4~6 个外围设备。

本文中的嵌入式系统由AT91ARM9200 处理器、Linux 操作系统和ALTERA 公司的 ACEX 系列的EP1K 所组成。

2 EP1K 的逻辑设计

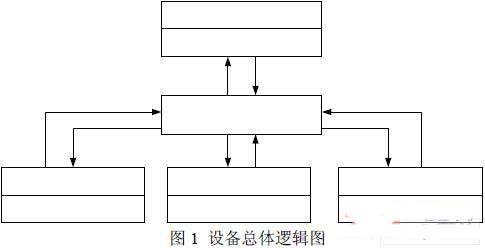

设计所要实现的功能是 AT91ARM9200 处理器通过EP1K 控制多个带有UART 接口的 外设。EP1K 中包含了多个逻辑模块如图1 所示,为了实现多个模块间的互联就需要片内总 线的支持,而本文采用的是WISHBONE 片内总线规范。

2.1 WISHBONE 总线设计

WISHBONE采用主从结构,也称之为SLAVE/MASTER 结构。主单元MASTER 是发起 与从单元SLAVE 之间的数据传输,MASTER 和SLAVE 通过握手协议来实现可靠通信的。

WISHBONE 总线架构提供了四种不同的互联方式:点对点(Point-to-point)、数据流(Data flow)、共享总线(Shared bus)和交叉开关(Crossbar switch)。为了实现单个MASTER 和多个SLAVE 的设计要求,同时要求总线结构占用较少的逻辑单元,所以采用了共享总线 的互联方式。

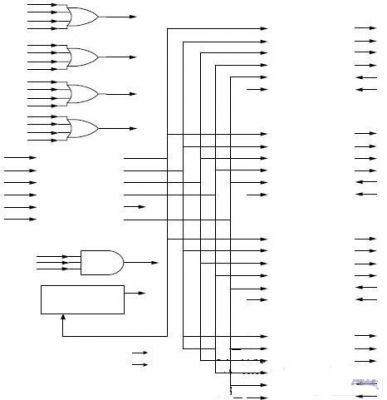

共享总线应包括 MASTER、SLAVE、INTERCON 和SYSCON 四个部分。MASTER 和 SLAVE 是实现总线信号与IP 核的信号转换,INTERCON 用于MATER 和Slave 的信号互联, 而SYSCON 则提供稳定的时钟信号和复位信号。总线逻辑结构如图2 所示,因为只有一个 MASTER,设计时就省略了对总线使用权的总裁。MASTER 的地址和数据总线分别与四个 SLAVE 相联,其它的控制信号也都是直接相连,而SLAVE 的选通是通过stb 信号实现。 SLAVE 的stb 信号是由地址译码产生SLAVE 选择信号s_sel、m_cyc 和m_stb 三个信号相与 的结果。所选通的SLAVE 将ack 信号置1 表明一个数据传输周期的正常结束并将数据锁存 或发送到总线上,而err 信号置1 表示非正常结束,rty 信号置1 表示要求数据重发。

图 2 WISHBONE 总线的逻辑结构图

总线的详细设计过程请参考 WISHBONE SoC Architecture Specification, Revision B.3,而 MASTER 和SLAVE 的设计可以参考OpenCores 的网站上相关设计。

2.2 UART 的逻辑设计

UART 的通信协议十分简单,以低电平作为起始位,高电平作为停止位,中间可传输 5~8 比特数据和1 比特奇偶校验位,奇偶校验位的有无和数据比特的长度由通信双方约 定。一帧数据传输完毕后可以继续传输下一帧数据,也可以继续保持为高电平,两帧之间 保持高电平,持续时间可以任意长。

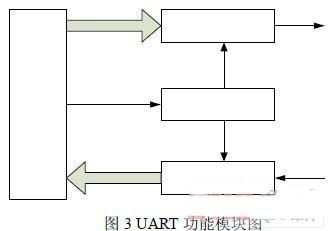

UART模块由SLAVE接口、波特率控制器、UART接收器和UART发送器构成。SLAVE 接口是为了实现WISHBONE 总线和功能模块之间的数据传输;UART 发送器的用途是将准备输出的并行数据按照基本UART 帧格式转为TXD 信号串行输出;UART 接收器接收RXD 串行信号,并将其转化为并行数据,但串并转换的时钟同发送器一样处理,收发设备间的时 钟是会累计的,会导致接收数据不正确,波特率控制器就是专门产生一个远远高于波特率的 本地时钟信号对输入RXD 不断采样,以不断地让接收器与发送器保持同步。

波特率控制器实际上就是一个简单的分频器。可以根据给定的系统时钟频率(晶振时 钟)和要求的波特率算出波特率分频因子。已算出的波特率分频因子作为分频器的分频数。 对于波特率发生器中的系数一般在FPGA 实现时往往是固定的,但对于不同的实现,这个 系数需要更改。波特率控制器产生的分频时钟,不是波特率时钟,而是波特率时钟的16 倍,目的是为了在接收事实进行精确地采样,以提出异步的串行数据。

UART 发送器由16 个字节FIFO 和信号发送器组成。FIFO 主要是起到数据缓存的作用, 信号发送器的核心部分由有限状态机实现的,实现伪代码如下:

case (状态机状态)

空闲状态:if ( FIFO 中有数据 )

状态机跳转到 FIFO 读取状态;

else

状态机保持空闲状态;

FIFO 读取状态:读取FIFO 数据,保存到移位寄存器;状态机跳转到开始位状态;

开始位状态:时钟计数,发送开始位;计数结束后状态机跳转到数据位状态;

数据位状态:时钟计数,发送数据,移位寄存器移位;计数结束后

if(移位寄存器内数据发送完毕)

状态机跳转到停止位状态;

else

状态机跳转到数据位状态;

停止位状态:时钟计数,发送停止位;计数结束后状态机跳转到 s_idle;

default:状态机复位到空闲状态;

endcase

UART 接收器包括了16 个字节FIFO、信号同步器和信号接收器三个部分。其中信号同 步器则是为了解决串行数据帧和接收时钟是异步问题,其它两部分和UART 发送器的中的 功能相似,只是数据传送的方向相反。

远程自动抄表系统 AT91ARM9200 UART模块 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)