FFT实时谱分析系统的FPGA设计和实现

时间:09-12

来源:电子技术应用

点击:

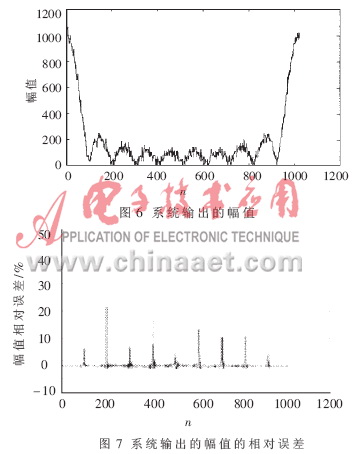

本FFT实时谱分析系统采用定点运算方案,输入为12位复数数据,输出为14位复数数据。采用方波信号进行测试,其参数为:脉冲幅度H=100,脉冲宽度M=10。本FFT实时谱分析系统输出的幅值如图6所示,输出的幅值的相对误差如图7所示。相对误差较大的一些点均出现在标准FFT输出的幅值很小的点上,这是由于有限字长效应引起相对误差造成的。同时由于采用的算术运算方案是定点运算,加剧了小信号的信噪比的恶化。但在实际应用中这些输出幅值很小的点会被判别为频谱上的噪声点,对实际的频谱分析影响不大,故对系统的误差影响并不大。而在标准FFT输出的幅值较大的点上,相对误差则很小。

本设计全部由VHDL语言实现,采用自顶向下的设计方法,完成了一个1024点FFT实时谱分析系统。该FFT采用了基-4原位算法,既保证了运算速度,又节省了硬件资源。该FFT通过CORDIC算法实现复乘,较传统的复乘运算节省了大量的ROM资源,同时采用了流水线结构,加快了运算速度。

参考文献

1 刘淩,胡永生. 数字信号处理的FPGA实现. 北京:清华大学出版社,2002

2 李广军,孟宪元. 可编程ASIC 设计及应用[M].成都:电子科技大学出版社,2000

3 刘朝晖, 韩月秋.用FPGA 实现FFT 的研究[J].北京:北京理工大学学报,1999;19(2):234~238

4 Volder J E.The CORDIC Trigonometric Computing Technique IRE.Trans.on Electronic Computer,1959(9)

FPGA 快速傅里叶变换 CORDIC算法 FFT 相关文章:

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)