基于速度匹配软件的网络芯片仿真方法

对微处理器、图形芯片或复杂设计的仿真通常要求降低目标系统的速度,因为即使快速FPGA也可能跟不上高速目标系统的速度,本文介绍一种基于速度匹配软件的网络芯片仿真方法,并指出采用这种新技术需要注意的事项,值得(中国)集成电路设计工程师关注。

在今天四通八达的宽带互联世界中,网络设备的智能、速度和集成度正变得越来越高,随着复杂度的增加,针对硬件设计的软件仿真 变得越来越费时,难度也越来越高。而采用软件仿真方法对实际状态和边缘情况进行建模的难度也在增加。这些问题的出现已经有段时间了,几乎所有微处理器厂商 都开始转用硬件仿真。但硬件仿真也有其弱点,硬件仿真不仅需要昂贵的无法随意更改物理层接口的专用硬件,还要求目标系统放慢速度,因此无法再现实际的运行 环境。

本文介绍第三种方案,该方案克服上述缺点,采用安装了速度匹配软件的标准PC,能够极大地加快并简化仿真过程,同时提供更接近实际情形的仿真结果,本文着重介绍采用最新的方法需要特别注意的地方。

设备仿真

仿真过程的第一步是将设计(通常是RTL级)装载进第三方厂商提供的仿真器。被仿真的设计再通过指形交叉连接器插入实际的母 板中,然后启动操作系统。最终测试将是运行一个实际应用,比如字处理器。当然,这种情况下仿真器的速度要比实际芯片慢好几个数量级,但这个过程确实是将设 计投入到了实际的运行中。随着近年来FPGA密度、速度和复杂度的不断提高,许多公司开始为他们的芯片创建定制的FPGA原型。

仿真微处理器、图形芯片或其它复杂的设计通常要求降低目标系统的速度,使之与较慢的仿真速度相匹配。即使是高速FPGA也 可能跟不上高速目标系统的速度。对于具有固定频率并独立于处理器的总线或必须以固定时间间隔产生的中断来说,目标系统速度太快会造成某些功能上的问题。一 般情况下,一个专用慢速目标板通常会通过慢速的外围设备与慢速仿真器进行通信。

但这种慢速解决方案并不适合用来仿真网络设备。对网络设备的仿真目的是要用真实的数据包测试在实际网络中运行的网络设备性 能,以确认新设计在实际环境下中的表现。一个网络一般由数十个、上百个-在因特网中-甚至是数百万个网络设备组成,要把所有这些设备的速度降下来是不现实 的。同时还有与网络有关的低层及高层时序约束条件。例如,连接以太网物理芯片与交换ASIC芯片的简化介质独立接口(RMII)就规定必须使用带特殊占空 比的50MHz时钟,而大多数商用仿真器无法以如此高的频率运行。更高层的协议要求设备确认数据包的到达,如果在规定时间内没有应答确认信号,数据包就会 重发。如果仿真器响应速度不够快,那么它就会被重复的数据包所淹没。

仿真接口也是一个问题。仿真器是一个纯数字的设备,而物理网络连接要求物理层对仿真信号进行整形,以使连接的对端能够正确 接收。同样,物理层接收到仿真信号后需要将它转换成数字信号。仿真器与网络直接相连时需要使用一个专门的仿真接口,用来将慢速数字信号转换成正确的仿真信 号。

这时的速度失配问题通常用硬件方法来解决,即电路板的一端是一个以太网适配器,另一端是与仿真器相连的数字接口,但这种解 决方案实施起来有一定的难度。首先,硬件的制造成本很高,并且需要较长的开发周期。向一个实际芯片问世后就失去用处的原型投入大量的人力物力是毫无价值 的。

其次,针对以太网、光纤信道或ATM等不同的网络接口需要设计不同的仿真电路,因此每个被测试的接口都需要不同的电路板。

第三,接口板上还需要用到缓冲器来存储因网络速度太快仿真器不能及时处理突发数据的问题。这些缓冲器将这些分组数据储存好后 再以较慢的速度送给仿真器。而管理这些缓冲器还需要使用相当复杂的状态机,这会给硬件实现带来很大的困难。此外,一旦接口板设计好后缓冲器的最大容量也就 固定下来了,今后要扩展的话还需要重新设计电路板。

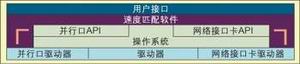

而下面的软件解决方案能更好地解决这一速度失配问题。此时被仿真的网络设备需要通过一台运行某种速度匹配软件的标准电脑再与 网络连接。仿真器则通过简单的并行口线与标准电脑的并行口相连,电脑与网络的连接则是通过标准的网络接口卡(NIC)。这种速度匹配软件不仅能够处理使网 络保持畅通的所有底层握手协议,也能正确处理并行口上的低层接口信号,从而使仿真器得以正确运行。速度匹配软件将来自于网络的数据包缓存于电脑内存中,因 此再大的突发数据包也不会丢失

- 使用NI PXI和LabVIEW实时模块有效简化硬件在环仿真系统(06-14)

- PCI总线智能GJB289A仿真卡设计(01-06)

- 导入灵活的FPGA验证方法(06-21)

- 测试SDRAM控制器的PDMA(01-04)

- 安捷伦展示3D-EM软件版本整合电路设计流程(05-27)

- 基于NI VeriStand和JMAG-RT进行高性能电机仿真(07-22)