用JTAG边界扫描测试电路板、BGA和互连

当第一批电路板样板放在硬件工程师桌面的时候,在测试时他会感到非常困扰。工程师耗费几个星期的时间设计电路图和布板,现在电路板做出来了,上面也安装好了元器件并拿在手上,现在必须确定它能否工作。工程师插上板子,加电并观察。但没有办法检测BGA下面微小到得用放大镜才能看清楚的芯片引脚,工程师应该怎么办?

BGA因为具有很多优点,所以应用非常普遍。然而我们不能靠剥离器件来探测BGA下面的连线。X射线是一种可选的测试方案,但是,它们仅仅 呈现焊点的静态图像,而不是提供确保连接性所需的动态电气报告,因而极难判断虚焊和可靠焊点之间的差异。人们总是希望一换掉BGA,问题就会消失。这通常 是一种昂贵和耗时间的选择方案,并且生产率非常低。

传统的边界扫描是另一种选择方案,但是这通常需要一些昂贵的工具,并要创建测试向量和测试执行,整个过程要花很长时间。所花费的时间长短取决于设计文档的稳定性和精度。此外,测试结果不是动态的,它们通常是对电路板上所发现问题的汇总。

最佳测试方案是存在于现有设计中的快速、简单和廉价的方案。许多BGA和大多数高端嵌入式处理器都支持通过IEEE 1149.1 JTAG接口进行边界扫描。

核心问题在于:信号线是否被正确地连接到物理上无法用探头接触的BGA器件的某一引脚?该信号线可能是时钟线、地址线、数据总线或任何感兴趣的信号线。关键是对其在电路中进行测试,以观察其状态是高、低或正发生状态跳变,以及信号线是否连通。

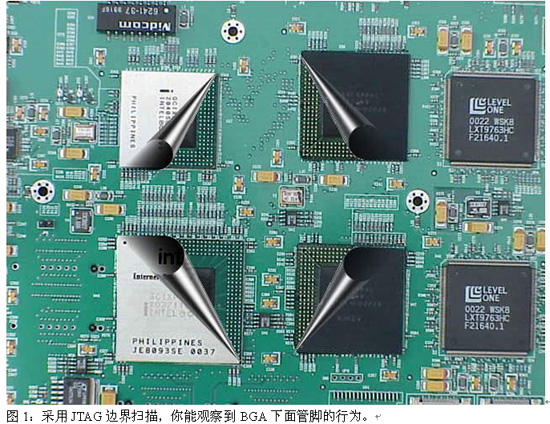

基于JTAG的边界扫描能以非传统的方式获得这些信息。概念很简单,即IC获取其所有引脚的状态并通过边界扫描链重复地把这些状态移出,并在个人电脑上同步显示结果。用户可以观察BGA器件下面每一个可扫描引脚的动态行为指示。

从显示器可以实时观察振荡器是否连接到G17脚或者地址或数据总线的行为,与此同时,电路板上的电路可以不受干扰而保持正常运行。该技术的 最好之处在于电路不知道你在进行测试,测试对电路的工作是完全透明的。测试应用程序以全速运行,在JTAG扫描链上的每一个器件都受到监测。

完成这类测试的工具非常依赖于图形用户接口(GUI)。一旦电路板被描述到应用软件中,屏幕上显示的芯片图就类似于电路版图中的封装。因 为芯片的JTAG接口可能以菊花链排列,版图可能仅包含一个处理器或一些BGA器件,或者可能包含许多器件,诸如处理器、门阵列、输入/输出控制器等。引 脚在屏幕上以彩色编码显示实时状况,如引脚现在的逻辑电平或是否在发生状态跳变。这就使测试非常直观。当测试目的是简单的连通性和状态检查时,就消除了创 建测试向量或测试执行的需要。

图1:目前市场上常见的JTAG调试工具

每一个器件都被发送JTAG指令EXTEST,以容许对器件上的每一根引脚进行完全的控制。应用程序然后可以驱动地址总线或切换到一根到连接器或LED的线,以检查整个电路的连通性,所有这一切只要点击鼠标就能完成。

所有具备JTAG端口的集成电路都将内建边界扫描功能,其组成部分包括:围绕被扫描器件边界的较长的移位寄存器和控制移位寄存器行为的状态机。在边界寄存器中的每一个寄存器位捕获或控制器件上每一个引脚的某些方面。如果该位是缓冲器使能的,该寄存器位就可能控制若干引脚。

软件应用程序引导状态机把每一个引脚的状态捕获到边界寄存器之中,然后将其移出JTAG端口。重复这个过程,并把结果显示在屏幕上,就可以实时显示在扫描链中的每一个器件的每一个引脚的行为。因为与测试向量法相比,通过显示图像可以做可视化分析,所以扫描速度不是问题。

对于典型的门阵列,一个这样的寄存器通常有300到400位;而对于处理器,最多有几千位。边界扫描描述语言文件(BSDL)定义了寄存器中每一位的含义。这些文件常见于IC供应商的网站,它们非常详细、精确地描述了边界扫描链中每一个单元的含义以及它与物理引脚的关系。

在器件中与每一个引脚相关的典型扫描单元有三种:1. 捕获/控制进入器件的信号;2. 捕获/控制流出器件的信号;3. 捕获/控制输出缓冲器使能。如果引脚是一个专用的"输入"引脚,它通常具有单个扫描单元。

JTAG接口只有4条线:测试数据输入(TDI)、测试数据输出(TDO)、测试时钟(TCK)和测试模式选择(TMS)。TCK是用于把数据读入TDI引脚并把数据读出TDO引脚的异步时钟。TMS引脚被用于转换TAP控制器的状态机。

BSDL文件是免费的,边界扫描电路已经被构建在你的JTAG器件之中,而

JTAG 相关文章:

- 采用边界扫描法测试系统级芯片互连的信号完整性(11-06)

- 满足的嵌入式系统电路特性测试需求的JTAG技术(11-07)

- 用于系统级测试和PCB配置的高级拓扑结构(05-16)

- 满足嵌入式系统电路特性测试需求的JTAG技术(04-25)

- 探讨基于JTAG技术的嵌入式系统测试的各个阶段(09-24)

- JTAG测试(02-23)